инженер программист плис что это

Junior FPGA Design Engineer: как стать?

Иногда начинающие разработчики не очень хорошо представляют, какую литературу надо читать для серьезного изучения того или иного языка.

Разработка под FPGA (ПЛИС) — это не просто какой-то язык. Это очень объемная область, с огромным количеством подводных камней и нюансов.

Что надо знать и уметь

Цифровая схемотехника

Синтаксис HDL-языка

Тестовые задания:

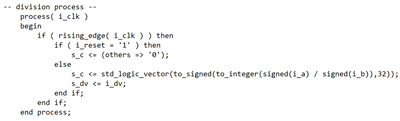

1. Нарисуйте схему из базовых цифровых узлов для следующего кода:

2. Нарисуйте поведение схемы из п.1 (т.е. состояния всех «переменных») при следующих входных воздействиях:

3. Напишите модуль для управления светофором, который будет зажигать красный, желтый и зеленый фонари во всем известной последовательности: красный, красный и желтый, зеленый, зеленый моргает, желтый, красный. Параметры, задающие время горения фонарей светофора и период мигания зеленого фонаря являются параметрами модуля. Время задается в количестве тактов синхросигнала clk_i.

Симулирование и верификация HDL-кода

Синхронный дизайн и всё, что связано с таймингами

Лекции и лабораторные

Я два семестра читал курс «Разработка под FPGA» для студентов старших курсов университетов Санкт-Петербурга. В курс входили как лекции, так и набор лабораторных работ. Лекции основывались на литературе, которую была перечислена выше.

К сожалению, это именно СЛАЙДЫ, которые мне помогали рассказывать лекции (не вся информация курса содержится на слайдах, некоторые я использовал как опору, а материал давался на доске).

Иногда будут видны картинки, которые никак не связаны с соседними (например, задания для тестов, которые давались на лекциях).

Классические ошибки

В этой части статьи я расскажу о типичных ошибках, которые допускают начинающие разработчики, и дам советы по их устранению.

Сделай шаг к ПЛИС

Ты ждал знак? Вот он!

Много лет я не решался начать программировать ПЛИС, потому что это сложно, дорого и больно (как мне казалось). Но хорошо, когда есть друзья, которые помогают сделать первый шаг. И теперь я не понимаю одного — ПОЧЕМУ Я ЖДАЛ ТАК ДОЛГО?

Сейчас я помогу сделать первый шаг и тебе!

А зачем оно мне?

Ты устал постоянно читать доки по своему МК или держать кучу информации в голове. Ты все переписал на asm, но скорости все равно не хватает. Ты подключил два внешних устройства к своему МК, подключаешь третье, но у тебя кончились прерывания, перестают работать те модули, что уже работали. Ты берешь другой МК, более мощный из той же линейки, но опять мануалы, регистры флагов, биты… ад. Меняешь платформу: переходишь на другой МК и выкидываешь на помойку свои знания по прежней платформе. Что бы ты не делал — оно дается тяжело. Ты находишь популярную платформу, в которой можно легко из компонентов собирать проект, но выше аппаратных ограничений данного МК все равно не удается прыгнуть… Где-то на краешке сознания иногда проскакивает мысль, что вот на ПЛИС это бы точно заработало быстро и параллельно, что это «именно та задача, которую бы надо решать на плис», но я стар/глуп/занят/etc чтобы суметь/начать такое делать.

Хочешь наконец вздохнуть свободно? Идем дальше!

Радость от разработки на ПЛИС

У меня был тяжелый рабочий день. С одной работы я приехал на вторую работу, потом на дачу, вечером домашние дела, уроки, потом семейный просмотр кино и только в 23 часа я оказался совершенно свободен! Сказать, что я был уставший — ничего не сказать. Но в таком состоянии я сел за ноут с твердой целью: сделать генератор меандра на 440 Гц. Прошло 20 минут и я уже слышал его в наушниках. Я не верил своим ушам! Еще 15 минут мне потребовалось, чтобы сделать ШИМ и менять громкость. К тому времени плата с ПЛИС у меня была всего с неделю и до этого я пролистал всего пару книг по Verilog.

В тот вечер я понял: ВОТ ОНО! Вот та платформа, в которой я быстро и легко могу превращать свои мысли в реально работающее железо!

Почему так?

Проблема выбора

Сильно останавливают вопросы, что выбрать: Altera/Xilinx, Verilog/VHDL, какую отладочную плату взять. Но обо всем по порядку.

Производитель

Я выбрал Altera. Почему? Ну мы вот так с другом решили, хотя название Xilinx мне красивее. НО. Если ты сейчас не можешь выбрать, то я сделаю это за тебя. Тебе нужен Altera! Почему? Я не знаю. Сейчас важнее сделать шаг: сделать выбор. Я выбрал Altera и пока не пожалел.

Берем Verilog — потомучто… ну ты понял.

Отладочная плата

На выбор отладочной платы ушло больше всего времени. Понятно, что платы отличаются установленной микросхемой ПЛИС. А микросхемы ПЛИС отличаются друг от друга количеством элементов. Но совершенно не понятно, сколько их потребуется для твоих тестовых проектов. Поэтому большую часть времени я потратил на поиск всевозможных проектов на ПЛИС на предмет того, чтобы узнать, сколько они потребляют ресурсов ПЛИС.

В семействе Altera, за разумные деньги мы можем купить платы с CPLD MAX II на 240, 570 и 1270 элементов, либо более старшие микросхемы FPGA, которые Cyclone 1, 2, 3, 4 с количеством до 10000 и более ячеек. Как же выбрать?

Даже на базе 240 ячеек, проект Марсоход делает просто огромное количество проектов. Настоятельно рекомендую ознакомиться, чтобы иметь примерное представление о сложности проектов, которые можно уместить в 240 ячеек. С другой стороны, существуют проекты, которые полностью программируются под аппаратную копию определенного ПК, включая процессор и всю логику вокруг него (NES, Speccy, Orion, ЮТ-88, etc). Для этого уже требуется пять, десять и более тысяч ячеек. Плюс эти платы содержат дополнительные внешние устройства.

Поэтому я бы посоветовать взять что-то среднее между 240 и 10000 ячейками, с предпочтением в сторону увеличения в зависимости от доступных средств. На отладочной плате лишние ячейки это не страшно, а если их не хватит — уже ничего не поделаешь. Потом, когда устройство отлажено, станет ясно, сколько надо ячеек, купить под нужное количество, без лишнего «обвеса», дешевле и оставить в готовом устройстве.

То, чем действительно отличаются MAX от Cyclone’ов, кроме количества ячеек, это:

1) У серии MAX внутри нет PLL. На каждой отладочной плате есть генератор, как правило на 50 МГц. Основной массе проектов этого будет достаточно. Все синхронизации будут происходить путем деления 50 МГц на какое-нибудь значение. Либо, можно взять внешний генератор и подать на отдельный вход ПЛИС. А что, если потребуется частота выше 50 МГц? Мне не удалось с ходу найти генераторы выше 50 МГц. Но тут как раз на помощь и приходит PLL, который встроен в Циклоны. На нем можно умножить частоту, например, до 100 МГц.

2) В серии Cyclone встроены аппаратные блоки умножения. Их количество зависит от конкретной модели — тут как раз можно «всетаки заглянуть в инструкции», чтобы узнать сколько. Если предполагаете делать какой-то ЦОС, то они пригодятся: сэкономят ячейки, увеличат скорость. С другой стороны, если нет умножителей, их можно синтезировать, но у маленькой ПЛИС на это может не хватить ресурсов.

Во всем остальном у меня критерий «влезло/не влезло». Отладка на заведомо бОльшей, чем нужно плате, с последующей заливкой в минимально необходимую для этого.

Сколько нужно денег?

Программатор

Я считаю, что у меня нет времени, чтобы паять программаторы на рассыпухе.

300 рублей. Я свой брал на ебее, выглядит так:

Отладочная плата

Выбор широкий, в зависимости от количества денег.

Начальный уровень 350 — 550 рублей. Это платы на MAX II (240 или 570 ячеек). Могут подойти для начального ознакомления и дальнейшего пристройства в конечные устройства. На плате есть генератор, пара кнопок, пара светодиодов, остальные 80 выводов на свое усмотрение.

Блок питания

Обязательно должен быть, но не всегда идет в комплекте. Потребуется БП на 5 вольт и ток 2А.

Средний уровень от 900 до 1500 рублей. Это платы Cyclone 1, 2, 3, 4 отличающиеся в основном количеством ячеек.

Маркируются примерно так:

EP2C5T144 — Cyclone 2 примерно 5к ячеек

EP4CE6E22C8N — Cyclone 4 примерно 6к ячеек

EP2C8Q208C8N — Cyclone 2 примерно 8к ячеек

Можно заметить, что Cyclone 3 может иметь больше ячеек, чем Cyclone 4.

Вот несколько вариантов:

835 рублей.

ALTERA FPGA CycloneII EP2C5T144 Minimum System Board for Learn good

880 рублей

Altera CycloneII EP2C5T144 FPGA Mini Development Learn Core Board E081

1265 рублей

EP2C8 EP2C8Q208C8N ALTERA Cyclone II FPGA Evaluation Development Core Board

Платы с расширенными возможностями. Это платы, на которых установлены дополнительные модули (UTP, USB, AUDIO), разъемы (SD, VGA), кнопки, переключатели, светодиоды, семисегментные индикаторы и т.д. Либо может идти базовая плата, а к ней могут прилагаться платы расширения отдельно.

Вот основная плата. На ней есть 2 светодиода, 2 кнопки, 4 переключателя, семисегментный интикатор и микросхема оперативной памяти.

Плата расширения. На ней распаяны SD, VGA, а так же контроллеры USB(High Speed USB2.0 Chip: CY7C68013A), AUDIO(Sound Card up to 96kHz/32bit ADC/DAC: WM8731S), UTP(100M Ethernet interface: DM9000A):

Эти платы просто вставляются одна в другую, но у меня она пока лежит в ящике. Для своих поделок у меня макетка, с которой я соединяюсь шлейфом, который идет в комплекте. Еще в комплекте идет блок питания на 5 вольт.

Altera Cyclone NIOS II SOPC FPGA Development Learning Board EP2C8Q208C8N+LCD1602 — 2670 рублей

Terasic Altera FPGA DE0-Nano Cyclone IV Development and Education Board — 4600 рублей

Но в целом, большие и дорогие отладочные платы я бы не рекомендовал сразу покупать. Дорогие покупки должны быть обоснованы, сейчас же пока не ясно что подойдет лучше. Ясно станет, когда начнется практика.

Заказал, ждем

Пока идут платы, можно начать себя морально и технически готовить:

— Установить Quartus II v.11.1

Почитать:

— Книга: А.К. Поляков Языки VHDL и Verilog в проектировании цифровой аппаратуры 2003

— www.kit-e.ru/articles/circuit/2008_3_161.php — Краткий курс HDL

— Уроки на марсоходе по верилогу, архитектура, простые советы по стилю.

— VERILOG как образ жизни

— Хорошие примеры (EN)

— Как начать работать с ПЛИС (Xilinx)

Мы ждем от тебя интересных проектов на ПЛИС!

PS. Обращаясь к тебе на «ты», я обращаюсь, как к равному, личности, а не части толпы. Если обращение на «ты» оскорбило, прошу меня извинить.

ВНИМАНИЕ! Verilog и ПЛИС не являются серебряной пулей и волшебным средством решения любых задач, они не могут заменить микроконтроллеры во всех проектах. Для работы с ПЛИС требуется определенный уровень технической подготовки. Вы сами несете ответственность за все решения в вашей жизни. Автор снимает с себя ответственность за возможные финансовые и временные потери, связанные с вашими исследованиями в области ПЛИС и Verilog.

Разработка на FPGA – Хорошая, плохая и отторгающая

Дата: 06.08.2020 10:57

На просторах интернета наткнулся на занятную статейку, которую может быть будет полезно прочитать, перед тем, как погружаться в мир FPGA

Введение

С каждым годом различные журналы и издательства по проектированию встраиваемых систем все чаще говорят о программируемых логических интегральных схемах (ПЛИС). Технология FPGA часто рассматривается как одна из самых мощных, но и одна из самых разочаровывающих этапов для разработчика встраиваемых систем.

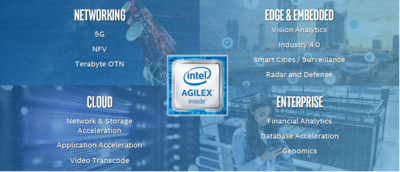

С каждым новым поколением FPGA становятся быстрее, имеют меньшую геометрию и меньшее потребление, увеличивается количество логических элементов, улучшается показатель стоимость/количество операций, возможности кажутся бесконечными. Однако с большой мощностью (и реконфигурируемостью) приходят, по крайней мере, с ПЛИС, некоторые серьезные проблемы обучения и разочаровывающие дни (недели) в офисе. Давайте поговорим о том, где сегодня находятся ПЛИС, где они были всего несколько лет назад, и о некоторых болевых точках, которые все еще существуют.

ХОРОШАЯ

Большие, реконфигурируемые, море логических ресурсов

Технология FPGA позволяет разработчику реализовать практически любой алгоритм и/или управление, которые ему требуются. Современная ПЛИС состоит из десятков, а то и миллионов логических элементов и триггеров, которые могут быть объединены вместе, чтобы реализовать всё: начиная от антидребезга для кнопки (denounce circuit) и заканчивая хост-контроллером x16 PCIe gen-3. Использование ПЛИС в вашем проекте дает вам почти бесконечную свободу для реализации любой необходимой вам функциональности.

Уровень абстракции

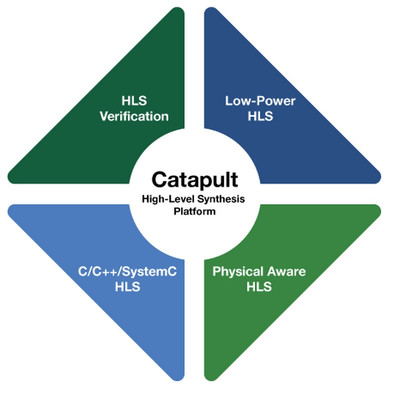

Представьте себе, что вы хотите спроектировать систему на логических микросхемах 74-ой серии, и люди, которые работали с первыми ПЛИС, должны были сделать почти то же самое. К счастью, сегодня нам не приходится думать на таком низком уровне. Существуют языки, называемые языками описания аппаратного обеспечения (HDL – Hardware Description Language), которые помогают разработчикам описать их алгоритм и передать его синтезатору, который затем создает список соединений логических выражений и регистров (нетлист). Кроме того, существует широкий спектр технологий и языков абстракции более высокого уровня. Xilinx предоставляет инструмент под названием Vivado HLS (HLS расшифровывается как high-level synthesis – высокоуровневый синтез), который позволяет разработчику писать на C, C++ или System C и затем из этого описания генерировать HDL код на языках VHDL или Verilog. Здесь, в Viewpoint Systems, мы часто используем технологию LabVIEW FPGA, которая позволяет описывать проект на ПЛИС с помощью графической среды программирования, использующей парадигмы потока данных.

Ресурсы и экосистема

Коммерчески доступные ПЛИС существуют с середины 1980-х гг. это долгий срок для развития технологии и её экосистемы. Существует множество ресурсов, доступных для всего: от понимания того, как устроен кремний, до того, как синтезатор генерирует нетлист, до лучших методологий описания HDL-кода для генерации логических структур, необходимых вам. Вы можете зайти на Amazon и поискать книги по ключевому слову FPGA и найдёте сотни доступных книг. Если вы загуглите слово FPGA, вы сможете найти десятки тысяч ответов на вопросы. Поскольку HDL является текстовым описанием, эти вопросы и ответы индексируются поисковыми системами, что делает поиск информации простым и быстрым.

Кроме того, за последние несколько лет появилось больше ресурсов об инструментах синтеза более высокого уровня, таких как Vivado HLS, Calypto/Catapult и LabVIEW FPGA.

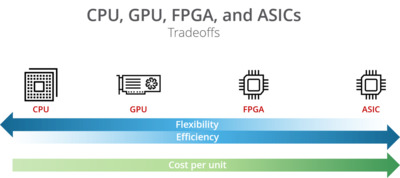

Скорость и размеры

Современные ПЛИС могут работать очень быстро – например, с частотой в сотни мегагерц. Вы можете подумать: «но, мой процессор Intel работает на гигагерцовой частоте!” Это правда! Однако ваш процессор Intel является «процессором общего назначения» – он делает большое количество вещей довольно хорошо, а не небольшое количество вещей действительно хорошо. ПЛИС позволяют писать массово параллельные реализации алгоритмов, при этом пропускная способность может быть в 10 раз, 100 раз или 1000 раз выше, чем любого процессора на современном рынке.

Хотя высокоуровневая абстракция отлично подходит для более быстрого вывода продукта на рынок (time-to-market ) вы просто никогда не сможете заставить свой проект работать так же быстро, как при написании кода вручную в традиционном HDL, таком как VHDL или Verilog. Языки абстракции и технологии высокоуровнего синтеза могут быть великолепны для быстрого создания прототипа; однако неизбежные накладные расходы всегда будут делать ваш проект более ресурсозатратным и, следовательно, более медленным (более низкая максимальная тактовая частота).

ПЛОХАЯ

Кривая обучения

“Это работает в симуляторе”

HDL-код по своей сути страдает от необходимости быть написанным и протестированным на другой платформе, в отличие от той, на которой он будет “запущен”. В случае VHDL очень легко написать VHDL-код, который прекрасно работает в моделировании, но никогда не будет работать в железе (загруженным в ПЛИС). Например, попытка сделать слишком много операций за один так (например, выполнение десятков или сотен операций умножения с накоплением (MAC) для фильтра с конечной импульсной характеристики (FIR)).

Маршрут проектирования на HDL выглядит примерно так:

1. Определите входы/выходы разрабатываемого модуля

2. Определите алгоритм и последовательность действий, которые должен выполнять разрабатываемый модуль

3. Составьте структурную схему или блок диаграмму различных частей проекта

4. Если возможно, распишите состояния конечных автоматов и транзакции

5. Напишите код

6. Проверьте синтаксис

7. Выполните моделирование

8. Проверьте корректность работы модуля

— Если не работает, вернитесь к шагу 5

9. Загрузите файл конфигурации в ПЛИС для тестирования

10. Убедитесь в корректности работы модуля в железе

— Если не работает, вернитесь к шагу 5

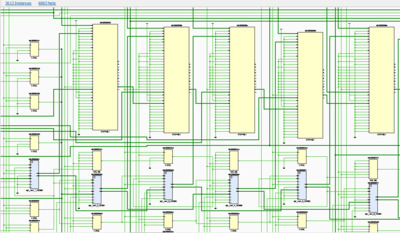

Кроме того, легко написать код, который породит огромное количество логики с помощью всего одной строки. Вот вам пример:

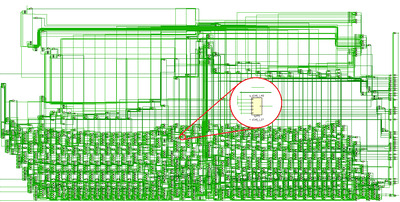

Приведенный выше код генерирует эту схему:

Vivado создала делитель, как мы и хотели, но для этого потребовалось почти 1800 логических ячеек. Сведение временных характеристик (таймингов) выполнения этой операции может оказаться очень сложным, особенно если она является частью других логических операций, которые должны произойти в том же такте.

ОТТОРГАЮЩАЯ

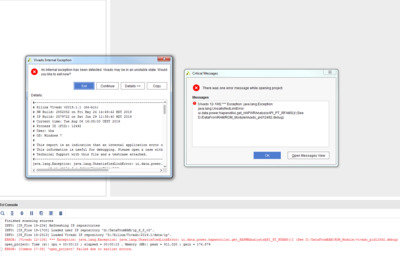

Не совершенность инструментов

Нет ничего более разочаровывающего, чем то, что среда разработки и ее инструменты не делают того, чего вы от них ожидаете или даёт непредсказуемые результаты. Хотя коммерческие ПЛИС существуют уже довольно давно, некоторые аспекты все еще отсутствуют. С последней версией инструментов Xilinx, Vivado, индустрия увидела большой скачок в функциональности и функциях. Это среда новая и она почти полностью заменяет их устаревшие среда разработки, при этом имеет свой собственный набор проблем и ошибок. Altera, производитель ПЛИС номер два, все еще работает с тем же программным обеспечением, который они используют уже более десяти лет.

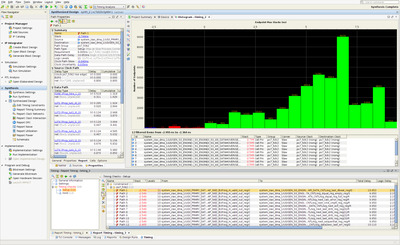

Сведение таймингов

Тайминги. Тьфу. Я, вероятно, провел большую часть времени, разочаровываясь в проектировании на ПЛИС, когда речь заходит о какой-то маленькой цепочки в нетлисте, которая просто отказывается соответствовать временным ограничениям, независимо от того, что я с ней делаю. Эти маленькие «занозы» появляются постоянно и лучший способ вытащить их – это просто накопленный годами опыт. У Xilinx есть их методология UltraFast Design Methodology, а у 2Altera много документации из серии «best practices», но на самом деле, когда дело доходит до этого, все сводится к написанию хорошего, небольшого, синтезируемого HDL кода. Но несмотря ни на что, вы окажетесь в ситуации, когда вам нужно создать экземпляр 32 чего-то там, и сведение таймингов будет вашим кошмаром.

ЛИЧНО ОТ МЕНЯ

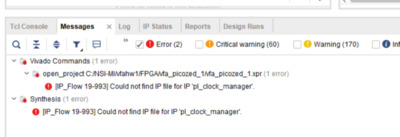

Несовместимость версий IP

Это, наверное, одна из самых раздражающих вещей при проектировании на ПЛИС. Несовместимость релизов среды разработки и используемых IP ядер. Да такое не очень часто случается, но это случается. Бывает так, что IP ядра обновляются, у них появляются новые возможности, но при этом они также могут быть переведены в статус устаревших и неподдерживаемых новой версией среды разработки. По этой причине, многие разработчики отказываются переходить на новую версию ПО в текущем проекте и предпочитают оставаться на изначально выбранной версии ПО. Как говориться, работает не трогай.

Долгая имплементация

Если проект по уровню немного выше среднего, то приготовьтесь к долгим перерывм между итерациями. Сложно сказать, это хорошо или плохо. С одной стороны многочасовая имплементация проекта даёт Вам кучу «свободного», которое можно потратить на написание документации, ревью кода, чтение литературы, просмотр ютубчика. Правда, когда это становится невыносимо, это может побудить разработчика на поиск способов сокращения времени имплементации и он откроет для себя инкрементную имплементацию, ECO-Flow, частичную реконфигурацию и много чего еще другого.

Но, когда горят сроки сдачи проекта, время необходимое на трассировку и размещение проекта, будет утекать как зарплата инженера-разработчика ПЛИС, что приведёт к куче пепла под Вашим рабочим местом, благодаря перегоревшему пукану и облысевшей/поседевшей голове.

Нужен мощный ПК

Современные среды проектирования требуют достаточно мощных (даже по современным меркам) компьютеров для комфортной работы. Не думайте, что если являетесь счастливым обладателем SSD и 16ГБ оперативы, то вам этого хватит. Боль и ужас от тормознутости интерфейса при таких параметрах заставят вас отказаться от покупки новой видеокарты для «Crysis на максималках» в пользу лишней планки и еще одного SSD для ваших ПЛИСовых проектов. Более того, если раньше для установки того же ISE вам бы хватило на «долгую счастливую жизнь» 10-20ГБ места на жёстком диске, то сейчас, только для установки желательно иметь не меньше сотни ГБ свободного места. Ну и под место под проекты не стоит забывать.

Я уверен, что мы что-то упустили, напишите в комментариях что именно и мы будем потихоньку дополнять эту статью новыми «радужными» аспектами проектирования на FPGA