jtag программатор что это

Обзоры JTAG программаторов

JTAG-программатор — устройство для записи программ, данных в память микроконтроллеров. Основное условие: микроконтроллеры должны поддерживать интерфейс JTAG — отладочный программно-аппаратный интерфейс, выполненный по стандарту IEEE 1149.1.

JTAG-программатор соединяется с компьютером кабелем, заканчивающимся разъемом USB. Через него поступает питание, происходит обмен информацией с компьютером. Сердце программатора — электронный блок с выходом на панель, в которую устанавливаются программируемые микросхемы.

Устройство не только записывает информацию в память микроконтроллеров, но и тестирует их работу. JTAG-программатор умеет взаимодействовать со средой разработки типа: ADS, IAR или WINARM. Что, в свою очередь, обеспечивает программирование и отладку микроконтроллеров с архитектурой ARM (7,9,11), Cortex М3 и подобных.

Обзор программатора для ПЛИС фирмы Altera. Кому интересно — прощу под кат.

ПРЕДУПРЕЖДЕНИЕ: данный обзор написан для тех, кто «в теме». Если об электронике и ПЛИСах Вы имеете смутное представление, то, судя по комментариям, этот обзор будет врятли Вам полезен.

Прошивка через JTAG: схема, распиновка, инструкция

Открываем для тебя дивный мир флеш-памяти

Содержание:

Ingredients

Directions

Что касается спутников ресиверов, то JTAG дает возможность перепрошить микросхему flash-памяти, если нет возможность прошить ресивер стандартным способом, через кабель к компьютеру. Сегодня мы разберем прошивку через JTAG-интерфейс на примере спутникового ресивера Globo X90 для его восстановления. Ранее мы уже научились прошивать его через кабель (см. предыдущую часть)

Зачем нужен JTAG

Прошивка через JTAG куда сложней обычной процедуры, поэтому к ней прибегают только в самом крайнем случае, когда ресивер совсем не подаёт признаков жизни: не загружается, не горит индикация, прошили другой прошивкой, либо после прошивки у вас только черный экран

JTAG прошивка по шагам

1. Собрать интерфейс (переходник) от порта ресивера к порту ПК

Собрать адаптер для JTAG не так сложно, как кажется на первый взгляд. Для Globo X90, да и вообще для всех ресиверов, предпочтительным вариантом сборки является вариант на микросхеме 74HC244N (её еще называют даташит). Распиновка JTAG:

Так выглядит собранная схема:

Со стороны ресивера это будет специальный разъём, он иногда даже так и подписан — JTAG

Второй «конец», который уходит в сторону ПК — это обычный LPT-кабель, который можно купить в любом компьютерном магазине. О том, как можно собрать всё это хозяйство:

3. Скачать программу для прошивки

Для реанимации ресиверов Globo и всех их клонов, а так же для Евросатов/Евроскаев потребуется специальный программатор. Что касается программного обеспечения, то на данных процессорах используется программа EJTAG_TT_1.0.6.17 (Я.Диск)

4. Установить драйвер, если у вас Windows XP

Если вы используете Windows XP, то необходимо установить драйвер giveio.sys (Я.Диск). Скопируйте файл драйвера GIVEIO.sys в папку C:\Windows\system32\drivers\ если, конечно, система у Вас установлена на диск С: и Вы не меняли пути установки Windows. Запустите файл install.reg.

5. Скачиваем прошивку

6. Переводим ресивер в отладочный режим

Обратите внимание на точки подключения. Они должны совпадать с тем, как вы собрали переходник. В некоторых Globo-ресиверах бывает обратная последовательность — не перепутайте. На некоторых ресиверах можно сделать обычную перемычку для перевода в отладочный режим

Можно использовать перемычку с IDE-винчестеров

Так это будет выглядеть:

7. Настраиваем EJTAG и прошиваем

Настройки в нашей JTAG tool выставляем так же как на скриншоте:

Если EJTAG не увидит ресивер, попробуйте поменять тип флеш памяти в последнем столбике. Вообще, здесь можно пробовать менять любые параметры, чтобы ресивер определился

Если после нажатия кнопки «коннект», у вас выходит ошибка «флэш ID нету в *.ini –файле», то попробуйте поменять настройки в программе, как и советовали выше, нужно попробовать все вариации галочек и точек в настройках. Если и это не приведет к успеху, то тут стоит насторожиться — проверить питание процессора, напряжение с БП — есть вероятность того, что флеш-память уже «умерла», тогда никакой JTAG уже не поможет. Следующим шагом жмём «Записать» и в окне проводника выбираем нужный файл с дампом или загрузчиком (лоадером)

[adace-ad >

При необходимости, как мы и писали выше, EJTAG сотрёт самостоятельно нужный блок памяти и начнет запись.

Здесь есть небольшой нюанс — достаточно залить около 50-70% прошивки через JTAG (желательно, конечно, полностью), но если у вас оборвалась прошивка на этом этапе, то можно попробовать прошивать стандартно (через порт), т.к. дальше уже идут списки каналов, спутники и так далее, т.е. то, что вы зальете и обычный прошивкой.

8. Убираем перемычку, отключаем Debug Mode

Не забудьте в конце прошивки корректно завершить программу EJAG, отключить от сети ресивер и аккуратно отключить JTAG-интерфейс. Так же снять перемычку для входа в отладочный режим. Далее подключаем ресивер уже через ком-порт и заливаем в него софт обычным способом.

Ручной поиск транспондера у спутника

Если вы заливаете «голую» прошивку, то есть необходимость вбить вручную нужные вам транспондеры. У некоторых ресиверов есть функция ручного ввода транспондеров. Для этого

Что такое JTAG и как это применить для тестирования печатных плат?

JTAG – это нечто большее, чем просто отладка и перепрограммирование микросхем

Если Вы применяли какие-либо инструменты, использующие JTAG, то Вы уже знакомы с этим интерфейсом. Например, процессоры часто используют JTAG для доступа к своим отладочным функциям, также все ПЛИС используют JTAG для перепрограммирования.

JTAG – это НЕ ТОЛЬКО отладка процессоров.

JTAG – это НЕ ТОЛЬКО программирование ПЛИС/CPLD.

Название JTAG чаще всего ассоциируется с инструментами отладки и перепрограммирования микросхем. Однако, в этих инструментах реализована только часть возможностей JTAG.

Эта часть возможностей, известная под названием Test Access Port или, сокращённо, TAP, является частью стандарта IEEE Std. 1149.1. Этот стандарт был разработан для тестирования сборок печатных плат (Printed Circuit Board Assemblies – PCBA) без необходимости доступа на так называемом «низком» (физическом) уровне, который требуется для анализа «сложных» случаев. Стандарт также не предусматривает разработку и использование специфических функциональных тестов. Изначально TAP был разработан только для взаимодействия с дополнительными регистрами, специально вставляемыми в микросхему с целью реализации данного метода тестирования.

Однако достаточно быстро производители микросхем заметили потенциал использования TAP и для других целей, например, для доступа к регистрам, предназначенным для отладки и перепрограммирования микросхем.

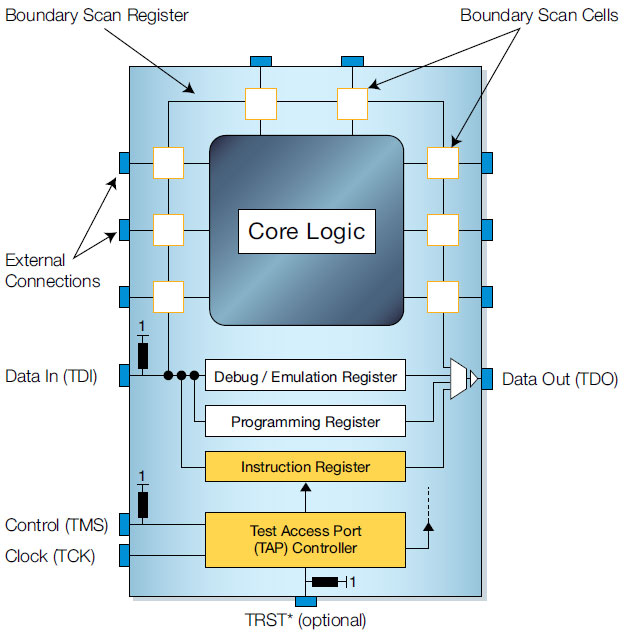

Теперь в микросхемы добавляется специальный регистр для тестирования через JTAG под названием Boundary Scan Register (BSR). Как и подразумевает название этого регистра, отдельные его части (или, по-другому, ячейки (Cells)) являются «пограничными» для микросхемы, так как располагаются между функциональным ядром и контактами корпуса микросхемы. По этой причине тестирование через JTAG часто называют пограничным сканированием (boundary scan).

Как технология пограничного сканирования, реализуемая стандартом JTAG, используется для тестирования печатных плат?

Ячейки регистра пограничного сканирования (Boundary Scan Register) могут работать в одном из двух режимов: 1) функциональный режим – ячейки не влияют на работу прибора, прибор работает в своём обычном виде; 2) тестирующий режим – ячейки отсоединяют функциональное ядро микросхемы от контактов корпуса. Тестирующий режим используется для управления значениями на контактах корпуса микросхемы (и в соответствующих цепях печатной платы), а также для считывания значений с подключённых цепей печатной платы.

Отключение функционального ядра микросхемы существенно упрощает разработку тестов, так как использование пограничного сканирования (boundary scan) позволяет не разрабатывать программу для микропроцессора или прошивку для ПЛИС и не включать прибор в «рабочем» режиме. Механизм управления и наблюдения за контактами корпуса микросхемы через четырёх-контактный TAP, JTAG интерфейс позволяет получить низкоуровневый доступ к контактам микросхемы для физического тестирования печатной платы.

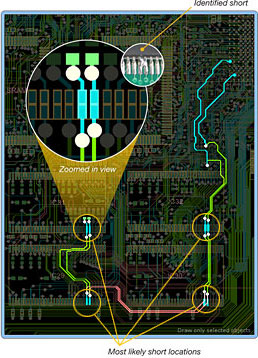

Существует два способа тестирования печатной платы при помощи пограничного сканирования (boundary scan). Первый способ – тест соединений (connection test). Он даёт хорошее покрытие, особенно для поиска таких неисправностей, как замыкания. Этот способ использует только возможности микросхемы с поддержкой JTAG, при этом тестируются соединения (например, пропайки) и цепи, а в случае применения системы XJTAG, тестируются ещё и логические функции платы. Второй способ – использование микросхемы с поддержкой JTAG для взаимодействия с микросхемами без поддержки JTAG, такими как DDR RAM или Flash память.

Что такое тест соединений (connection test) через JTAG?

Тест соединений (connection test) проверяет, соответствует ли изготовленная печатная плата исходному проекту, а также наличие на ней не предусмотренных проектом разрывов цепей или лишних замыканий.

Если согласно проекту какие-то контакты микросхемы должны быть соединены где-то на плате, то можно проверить факт наличия соединения, подавая значения на один из контактов и считывая с других. Если согласно проекту контакты микросхемы НЕ соединены, то можно проверить, нет ли между ними лишнего замыкания, подавая на один из них значения и проверяя, что на остальные это не влияет.

Кроме того, тест соединений (connection test) позволяет обнаружить отсутствие нужных подтягивающих резисторов, и «залипания» сигналов. Это также делается путём выставления на контактах определённых значений и сравнения считанных значений с заданной таблицей истинности.

Система XJTAG на основе нетлиста печатной платы и информации, считанной с поддерживающих JTAG микросхем, полностью автоматически генерирует тестовые вектора для проведения теста соединений (connection test) всей платы.

Что же делать с остальными микросхемами на плате, которые не поддерживают JTAG?

Как правило, основные микросхемы на плате, такие как процессоры и ПЛИС, поддерживают JTAG, но существует множество вспомогательных микросхем, которые JTAG не поддерживают. Как пример можно привести такие микросхемы, как ЦАП, АЦП, DDR, SDRAM, SRAM, Flash, Ethernet контроллеры, температурные сенсоры, генераторы частот и многое другое.

Тест соединений (connection test) позволяет проводить тестирование на замыкания цепей между микросхемами с поддержкой JTAG и микросхемами без поддержки, при этом достигается хорошее покрытие. Однако протестировать обрывы в таких цепях уже не получится.

С целью тестирования на наличие обрывов цепей между микросхемами с поддержкой JTAG и микросхемами без таковой, требуется использовать так называемые функциональные тесты. Если функциональные тесты пройдены, то это означает, что обрывов быть не может. Функциональные тесты могут быть как очень простыми, например, включение светодиода и ожидание подтверждения от оператора, что светодиод действительно загорелся, так и посложнее, например, запись данных в память, считывание их же и сравнение считанных данных с ожидаемыми.

Насколько сложно подготовить JTAG тесты?

При помощи библиотеки тестов для стандартных микросхем без поддержки JTAG, поставляемой с системой XJTAG, возможна подготовка и запуск набора функциональных тестов без необходимости программирования. Библиотека тестов содержит тесты как для простых элементов, таких как резисторы и буферные элементы, так и для сложных микросхем, таких как память DDR3 и так далее.

Т.к. пограничное сканирование (boundary scan) отключает контакты корпуса микросхемы от функционального кремниевого ядра, единая тестовая модель может быть использована для управления периферийными микросхемами вне зависимости от того, какая микросхема с поддержкой JTAG использована.

Как правило, в печатную плату не требуется вносить никаких изменений, так как большинство плат уже содержат JTAG контакты для отладки процессоров или программирования ПЛИС.

Что ещё нужно для использования микросхем с поддержкой JTAG?

Для тестирования печатной платы при помощи пограничного сканирования (boundary scan) требуется для каждой микросхемы с поддержкой JTAG скачать с сайта производителя микросхемы так называемый BSDL-файл – Boundary Scan Description Language. Это текстовый файл, описывающий назначения ножек корпуса микросхемы.

Используется ли JTAG тестирование в основном на производстве?

Не совсем. Одним из важнейших преимуществ тестирования через пограничное сканирование (boundary scan) является тот факт, что из дополнительного оборудования требуется только JTAG контроллер. Другие технологии тестирования, такие как летающие щупы (flying probe), рентгеновское сканирование, многозондовое тестирование (bed-of-nails) и так далее требуют наличия дорогостоящего оборудования, которое не всегда доступно.

Использование пограничного сканирования (boundary scan) при первом тестировании позволяет проводить тестирование более уверенно, так как не требует включения платы в основной режим работы и даже может быть выполнено ещё до окончания разработки «прошивки». Эти же тесты, разработанные при проектировании, могут быть использованы и на производстве.

Почему следует использовать пограничное сканирование через JTAG для тестирования печатных плат?

С увеличением доли микросхем, реализованных в корпусе BGA (Ball Grid Array), применение традиционных систем тестирования печатных плат, таких как многозондовое тестирование (bed-of-nails) или летающие щупы (flying probe) становится всё более ограниченным, так как «внутренние» контакты физически недоступны.

Пограничное сканирование (boundary scan) на основе JTAG при помощи простого «четырёхконтактного» интерфейса позволяет произвольно управлять контактами корпуса микросхемы с поддержкой JTAG, в том числе считывать значения, не имея к контактам физического доступа.

Стенд

В процессе проектирования и отладки временны́е и денежные затраты на разработку/приобретение испытательных/отладочных стендов могут быть очень существенными, а в некоторых случаях и превышать затраты на само проектирование. Во многих случаях использование пограничного сканирования (boundary scan) позволяет вообще отказаться от применения испытательного стенда, а в остальных случаях подойдет и значительно более простой и дешёвый стенд.

Малые партии

В случае, когда у компании имеется много проектов плат, выпускаемых малыми партиями, задача удешевления тестового оборудования особенно актуальна. Единственно приемлемым вариантом в данном случае является покупка системы «летающие щупы» (flying probe), но если цена при этом делится на все проекты, то временны́е затраты на подготовку теста для каждого проекта остаются неприемлемыми. Использование пограничного сканирования (boundary scan) позволяет ускорить подготовку теста для каждого проекта, при том, что покупка дорогостоящего тестового оборудования теперь не требуется.

Стоимость разработки теста

Так как разные микросхемы (процессоры и ПЛИС) взаимодействуют с периферией разными способами, разработка традиционного функционального теста отдельно для каждой платы является очень затратной. Пограничное сканирование (boundary scan) существенно сокращает стоимость разработки тестов благодаря упрощённому способу управления контактами корпуса микросхемы для взаимодействия с остальными компонентами на плате. А унифицированный интерфейс JTAG позволяет формировать отдельные тесты как библиотечные элементы и использовать их в разных проектах вне зависимости от применяемых микросхем с поддержкой JTAG.

И для тестирования и для программирования

JTAG часто применяется для программирования микросхем (ПЛИС) на плате в процессе производства. А если к программированию дополнительно добавить тестирование платы через так называемое пограничное сканирование (boundary scan), то получится существенно сэкономить время и упростить производство.

Использование на производстве тех же тестов, которые применялись при проектировании

Обычно для тестирования изделий на производстве применяется большое дорогостоящее оборудование. Всё, что требуется для применения пограничного сканирования (boundary scan) через JTAG – это контроллер XJLink, размерами сопоставимый с компьютерной мышью.

Удобная диагностика неисправностей

Пограничное сканирование (boundary scan) через JTAG, в отличие от специально разработанных функциональных тестов, позволяет получать информацию о точном месте возникновения неисправности, что очень помогает при восстановлении платы. А применение системы XJTAG ещё и позволяет визуализировать место неисправности на плате и указать точное место в принципиальной схеме.

Восстановление нерабочих плат, где функциональные тесты бессильны

Пограничное сканирование (boundary scan) через JTAG можно использовать на плате, где не работает ничего, кроме самого JTAG интерфейса. Если плата не включается, то провести традиционные функциональные тесты не получится. Простейшая неисправность в таких элементах на плате, как память или генератор синхросигнала не позволят применить функциональный тест, но легко обнаруживается при помощи JTAG.

Ещё статьи

Концепция применения JTAG

Посмотрите, на что способен JTAG (Английский)

Технические подробности JTAG

Обзор аппаратной реализации JTAG

Руководство по улучшению тестопригодности (DFT)

Рекомендации по улучшению покрытия платы тестами (Английский)

JTAG-тестирование при помощи XJTAG

Как XJTAG расширяет возможности JTAG (Английский)

JTAG в каждый дом: полный доступ через USB

Исследователи Positive Technologies активировали аппаратную отладку (JTAG) для Intel Management Engine, которая позволяет получить полный доступ ко всем устройствам PCH (Platform Controller Hub), используя технологию Intel DCI (через интерфейс USB). Мы планируем поделиться подробностями на одной из ближайших конференций. А о том, как активировать этот интерфейс, но для основного процессора, расскажем ниже.

От ошибок никто не застрахован. Это утверждение касается и низкоуровневого программирования, где таких привычных средств, как отладочная печать или программный отладчик, в определенный момент может быть уже недостаточно. Для решения этой проблемы разработчики аппаратных средств используют так называемые внутрисхемные эмуляторы (in-circuit emulators) или специальный отладочный интерфейс JTAG, если он присутствует на целевой платформе (IEEE1149.1 [1]). Эти отладочные механизмы появились еще в 80-х годах прошлого века [2]. Со временем производители микросхем расширяли возможности этих интерфейсов. Благодаря этому разработчики смогли получать детальную информацию об энергопотреблении, находить узкие места в высокопроизводительных алгоритмах и получили много других возможностей.

Для исследователей безопасности аппаратные средства отладки также представляют интерес. Они позволяют получить низкоуровневый доступ к системе в обход основных средств обеспечения безопасности, изучать поведение целевой платформы и ее недокументированные возможности. Очевидно, что подобные возможности оказались привлекательны и для спецслужб [3].

Долгое время доступ к этим технологиям для процессоров Intel имелся только у ограниченного круга лиц, что было связанно с необходимостью использования дорогого специализированного оборудования. Но с выходом процессоров семейства Skylake ситуация кардинально изменилась: отладочные механизмы были встроены в PCH [4], что позволяет использовать столь мощный инструмент обычным пользователям — включая и злоумышленников, которые могут таким образом получить полный контроль над процессором. Из соображений безопасности по умолчанию эти механизмы не активированы, но в данной статье мы покажем, что их можно заставить работать на оборудовании, которое доступно в обычных компьютерных магазинах.

Эволюция отладочных средств на процессорах Intel

1. От in-circuit emulator к JTAG

Первоначально in-circuit emulator (ICE) для процессоров Intel 80286 представлял собой отдельный компьютер («большую синюю коробку» [5]), который включал клавиатуру и монитор. ICE подключался вместо процессора отлаживаемой системы и эмулировал его поведение. Такой эмулятор позволял устанавливать точки останова, изменять память и регистры процессора, производить запись и чтение.

Позднее Intel представила новый аппаратный отладчик I2ICE (рис. 1), который уже не заменял собой штатный процессор. С помощью специальных переходников пользователь подключался к отлаживаемой системе, а для общения с хост-машиной такой аппаратный отладчик использовал стандартный последовательный порт на скорости 9600 Бод [5].

Рис. 1. Intel I2ICE — один из первых внутрисхемных отладчиков для процессоров Intel 80386 (recycledgoods.com/intel-series-iv-emul-system-iii514b.html)

По мере развития технологий и увеличения тактовых частот Intel отказывается от разработки отдельных полнофункциональных средств отладки и частично переносит ее внутрь процессора, в виде специального недокументированного режима ICE-mode (который по принципам работы очень напоминал другой режим — System Management Mode (SMM), у некоторых разработчиков того времени было стойкое убеждение, что SMM — не что иное, как документированный и расширенный ICE-mode [6]). В свою очередь, всеобщая стандартизация отладочных механизмов в электронной промышленности приводит к тому, что в некоторых процессорах Intel 80486 появляется поддержка тестового интерфейса IEEE1149.1 (JTAG) [7].

Joint Test Action Group (JTAG) на самом деле является названием рабочей группы, которая разработала стандарт Standard Test Access Port and Boundary-Scan Architecture (IEEE1149.1 [1]). Он позволяет использовать стандартную аппаратуру тестирования и отладки для широкого класса устройств. Со временем сокращение JTAG стало ассоциироваться со стандартом IEEE1149. В современных микросхемах он широко распространен в промышленности и используется для тестирования, прошивки, отладки и выходного контроля микросхем при производстве. Физически JTAG представляет собой четыре или пять выделенных линий, которые образуют тестовый порт TAP (Test Access Port). Стандарт предусматривает объединение устройств в цепочку, позволяя получать доступ к каждому подключенному устройству (рис. 2).

Рис. 2. Объединение отлаживаемых устройств в JTAG-цепочку

Часто разработчики аппаратуры расширяют базовую функциональность JTAG, вводя новые возможности; процессоры Intel не стали в этом смысле исключением, начиная с Pentium появляется более дешевый и мощный вариант внешнего отладчика, который использует специальный зондовый режим (probe mode).

2. Режим зондовой отладки

Режим зондовой отладки (probe mode) является еще одним недокументированным режимом работы процессоров Intel. Он используется для диагностики и отладки. Его невозможно активировать без доступа к JTAG-регистрам процессора. В probe mode процессор может изменять память, производить запись и чтение из портов ввода-вывода. В данном режиме прерывается нормальное выполнение инструкций и процессор переходит в режим бездействия, ожидая команд по интерфейсу JTAG. Такое поведение принципиально отличает данный механизм от ICE-mode, когда инструкции на процессоре продолжали выполняться. При входе в probe mode останавливается предварительная выборка и декодирование команд. Команды от JTAG для модификации или чтения поступают непосредственно в исполнительные блоки процессора, тем самым минуя этапы предварительной выборки и декодирования [8], что позволяет получать доступ к ряду регистров, которые недоступны из обычных режимов.

Probe mode реализован как расширение JTAG с добавлением нескольких регистров и дополнительных сигналов R/S#, PRDY (подробнее о том, как реализован режим probe mode, см. [8], [9]). Сторонние компании наравне с Intel выпускают JTAG-адаптеры для процессоров x86, в которых обеспечивается поддержка этого расширения, но мы рассмотрим только оригинальные аппаратные средства отладки.

3. Современные аппаратные средства и технологии отладки процессоров Intel

Современные процессоры Intel предоставляют JTAG через три интерфейса:

Рис. 4. Типы подключения DCI

Рис 5. Intel SVT Closed Chassis Adapter

Интерфейс Intel ITP-XDP имеет закрытый протокол, требует специализированного разъема на плате и специализированного программного обеспечения Intel System Studio (на сайте производителя доступна пробная версия). К недостаткам также стоит отнести высокую цену (около 3000 долларов США) и необходимость подписывать документы о неразглашении информации (Corporate Non-Disclosure Agreement) [10]. Высокая цена и CNDA делают данный отладчик недоступным для рядового разработчика или домашнего использования.

Однако начиная с процессоров семейства Skylake Intel внедрил технологию Direct Connect Interface (DCI), ее достаточно поверхностное описание можно найти в документации [4]. Данная технология ставит своей целью упростить разработку мобильных устройств, из чего вытекает ее недостаток: ее можно активировать без каких-либо аппаратных модификаций (при наличии JTAG линий между PCH и CPU). Также стоит отметить, что подключение с использованием адаптера Intel SVT использует линии USB 3.0, но реализует свой протокол, что позволяет работать с целевой системой в режимах глубокого сна. К сожалению, адаптер SVT при своей относительно низкой цене (390 долларов США) также доступен для покупки только после подписания CNDA.

Самым интересным для рядового программиста вариантом, который при этом не требует подписания каких-либо документов перед использованием, является USB3 Hosting DCI. Он представляет JTAG-интерфейс через обычный отладочный кабель USB 3.0. При активации DCI на целевой системе порт USB 3.0 переходит в режим slave и начинает принимать команды от хостовой системы.

Один из важных вопросов относительно USB 3.0 DbC DCI Hosting заключается в том, через любой ли внешний порт USB 3.0 возможно подключение к DCI — или требуется отладочный порт, доступный только на специальных системных платах для разработчиков. Следует рассмотреть данный вопрос подробнее.

В среде системных разработчиков существует путаница, порожденная тем, что сама по себе отладка через USB появилась достаточно давно (со времен USB 2.0) и в данный момент используется многими разработчиками для программной отладки ядер операционных систем и UEFI приложений. Однако программная отладка через USB (в windbg, UEFI debug agent и т. п.) не имеет ничего общего с механизмами аппаратной отладки через JTAG, кроме собственно транспорта. Спецификация контроллера шины USB 2.0 (EHCI, Enhanced Host Controller Interface) предоставляет специальный механизм, который называется Debug Port (PCI capability), с помощью которого возможно взаимодействие между сервером (программным или аппаратным) на отлаживаемой машине и клиентом на хосте. В частности, ядро Windows поддерживает отладку через EHCI Debug Port (при этом нужен отладочный кабель USB 2.0, с интегрированным устройством USB 2.0). При этом, действительно, не каждый внешний порт USB 2.0 мог работать как Debug Port, а эта возможность была закреплена за определенными портами, которые могли быть и не выведены наружу. Все зависело от производителя оборудования. Поэтому разработчики специально искали оборудование с выведенным наружу Debug Port, для отладки по USB. Таким образом, Debug Port — это атрибут USB-порта.

Однако ситуация полностью изменилась с появлением USB 3.0 и спецификации контроллера этой шины XHCI (eXtended Host Controller Interface). Данная спецификация также поддерживает отладку по USB, однако она претерпела существенное развитие и стала называться USB Debug Capability (DbC). Согласно XHCI, DbC является не атрибутом порта, а свойством конкретного контроллера XHCI. То есть, если данный XHCI-контроллер поддерживает DbC, то возможность отладки по USB 3.0 будет доступна на любом (в том числе и внешнем) порте USB 3.0. При этом DbC автоматический выберет первый порт, к которому подключен отладочным кабелем клиент, выполняющий транзакции USB 3.0.

Здесь важно отметить, что первые XHCI-контроллеры не поддерживали DbC, поэтому на системах с такими котроллерами отладка по USB была невозможна. Однако в PCH версии 100 и выше (для Skylake) компания Intel встроила свой собственный контроллер XHCI, который поддерживает DbC. Технология Intel DCI (которая и появилась начиная с процессоров Skylake) использует USB 3.0 DbС в качестве транспорта, для подключения JTAG-клиента. USB 2.0 Debug Port он не использует.

Таким образом, через любой порт USB 3.0 можно подключиться к DCI и осуществлять JTAG-отладку.

Активация DCI

Как же можно активировать этот отладочный интерфейс? Мы нашли три способа:

1. Активация через EFI Human Interface Infrastructure

EFI Human Interface Infrastructure — специальный механизм, который позволяет создавать пользовательский интерфейс в UEFI, обрабатывать и контролировать пользовательский ввод. Если посмотреть строение современных UEFI BIOS, можно найти в них множество скрытых опций, которые недоступны пользователю, но обрабатываются. На этом и основан наш первый способ. EFI HII определяет значения по умолчанию для всех опций, в том числе и скрытых. Найдя опцию, связанную с DCI, можно ее активировать для настройки по умолчанию, а затем, установив в BIOS заводские настройки, активировать DCI. Отредактировать эти настройки позволяет утилита AMI BIOS Configuration Program 5.0. Отредактированный образ программируется в SPI-flash программатором или через штатный механизм прошивки BIOS, если позволяют права доступа.

Однако у этого способа есть недостаток: система не загрузится, если активирован Boot Guard, так как утилита изменяет модуль EFI.

2. Активация через Flash Descriptor Region

3. Активация через P2SB-устройство

В конце концов, можно попробовать действовать напрямую — через устройство P2SB. В документации на разные поколения PCH можно найти специальный индекс и регистр, используя который можно активировать DCI на лету, если BIOS не заблокировал изменение настройки DCI.

Данный способ является уязвимостью, так как если BIOS не блокирует запись в регистр ECTRL, то из-за особенностей работы (возможности сохранения конфигурации между перезагрузками после выключения питания) позволяет активировать DCI один раз, а далее использовать JTAG-интерфейс как аппаратный backdoor в систему (например, отключать экран блокировки).

Мы провели исследование [12], в результате которого выяснилось, что крупнейшие производители материнских плат не устанавливают блокировку данного регистра, что позволяет активировать DCI и использовать этот механизм, например, для перезаписи BIOS в обход всех средств защиты, включая проверку цифровой подписи.

Резюме

Наличие отладочных механизмов в современных процессорах Intel позволяет облегчить разработку модулей UEFI, операционных систем, гипервизоров. Исследователи безопасности получают низкоуровневый механизм привилегированного доступа к аппаратуре, который может быть использован для поиска зловредного ПО, исследования недокументированных возможностей аппаратуры или драйверов специфического оборудования. Но, как любой отладочный механизм, DCI может использоваться и злоумышленниками для несанкционированного доступа к данным.

В качестве защиты от таких атак мы рекомендуем активировать Boot Guard, проверять бит активации DCI и запрет отладки в регистре IA32_DEBUG_INTERFACE (при этом DCI может работать, но остановить выполнение уже нельзя, поэтому нет возможности получить доступ к памяти и регистрам).