как установить xilinx ise на windows 10

Fenghe’s Blog

How to Install Xilinx ISE 14.7 on your Windows 10 PC

Xilinx ISE is an IDE(Integrated Development Environment) for Designing CPU. The installation curve is a little bit steep so I write this tutorial here.

NOTE: The connection to a Xilinx FPGA board is not supported on Windows VM(Virtual Machine) running on macOS or even with the aid of BootCamp as a dual system.

Download & Install the image

You can search on Google with the keywords “Xilinx ise 14.7 google drive”, then you should find some result like the following. Download it and install it as you would do with other programs.

You can use IDM(Internet Download Manager) to speed up your download.

During the installation, you should be aware that to finish the default installation process, you should have MATLAB no later than 2017b installed on your PC.(2018a, 2018b, 2019a, 2019b may not work, as I dare not to try)

HOLD ON! How about activating the software?

Get the License

Download the license at here, and load it upon finishing the installation.

Fix Some Potential Crash

After the installation, you might be unable to open or even create a project. To solve that, you should follow the following instructions

For more information, you can jump to the original article.

Как установить xilinx ise на windows 10

Набор инструментария ISE Design Tools для проектирования CPLD/FPGA от Xilinx позволяет установить и использовать некоторые функции и возможности бесплатно. Этот режим установки пакета ISE Design Tools называется ISE WebPack.

Xilinx ISE это интегрированная среда разработки (ISE расшифровывается как Integrated Synthesis Environment), набор программных инструментов от компании Xilinx, предназначенный для синтеза и анализа разработок на языке описания логических схем HDL. Этот набор инструментов позволяет разработчику синтезировать («компилировать») свои разработки, выполнять анализ их работы по интервалам времени, проверять диаграммы RTL (register-transfer level), симулировать реакцию разрабатываемой логики на разные воздействия, и конфигурировать целевое программируемое устройство (CPLD, FPGA) с помощью программатора (адаптера JTAG, так называемого «кабеля Xilinx»).

Система разработки Xilinx ISE жестко привязана к архитектуре чипов программируемой логики компании Xilinx, и она не может использоваться для чипов логики других производителей. Xilinx ISE главным образом используется для синтеза и разработки схем, в то время как ISIM или ModelSim logic simulator используется для тестирования на уровне системы. Другие программные компоненты, поставляемые с Xilinx ISE, включают Embedded Development Kit (EDK), a Software Development Kit (SDK) и ChipScope Pro.

С 2012 года Xilinx ISE больше не поддерживается, так как усилия специалистов Xilinx были перемещены на разработку продукта разработки Vivado Design Suite, который выполняет те же самые функции, что и ISE, с некоторыми дополнительными возможностями для разработки систем и чипов. Xilinx выпустила последнюю версию ISE в октябре 2013 (версия 14.7).

[Интерфейс пользователя]

Основной интерфейс пользователя в ISE представляет Project Navigator, который включает отображение иерархии разработки (Sources), редактор исходного кода (Workplace), выходную консоль (Transcript) и дерево процессов (Processes).

Иерархия дизайна состоит из файлов дизайна или модулей, зависимости которых друг от друга в ISE отображаются структурой дерева. Для разработок в одном чипе может быть один главный модуль, и все другие модули подключаются к нему, что похоже на функцию main() в программах C/C++. Привязка логики к выводам чипа и ограничения по времени называется «ограничениями дизайна» (Design Constraints), что указывается в модулях.

Иерархия процессов описывает операции, которые ISE выполняет для текущего активного модуля. Иерархия включает функции компиляции, их функции зависимости (dependency functions) и другие утилиты. Это окно также обозначает проблемы или ошибки, которые возникают с каждой функцией.

Окно консоли (Transcript) предоставляет информацию о состоянии текущих выполняющихся операций, и информируют инженеров о проблемах дизайна. Отображение проблем может быть отфильтровано для того, чтобы показывать только предупреждения (Warnings) или только ошибки (Errors), или показывать все вместе.

[Симуляция]

Тестирование на уровне системы может выполняться с помощью утилиты ISIM или ModelSim logic simulator, и такие тест-программы могут также быть написаны на языках HDL. Программы тестирования могут включать симулированные входные сигналы определенной формы, или точки мониторинга, в которых можно наблюдать или проверять выходные сигналы устройства, проходящего тест.

ModelSim или ISIM могу использоваться для выполнения следующих типов симуляций:

• Проверка работы логики, чтобы гарантировать получения от модуля ожидаемых результатов.

• Проверка поведения схемы, чтобы убедиться в отсутствии ошибок логики и проблем с интервалами времени.

• Симуляция размещения и маршрутизации логики на кристалле (Post-place & route simulation), чтобы проверить поведение системы после размещения логики в ресурсах кристалла перепрограммируемой логики CPLD или FPGA.

[Синтез]

Патентованные алгоритмы Xilinx для синтеза логики позволяют реализовывать дизайн на 30% быстрее аналогичных конкурирующих программ. Высокая плотность упаковки логики на кристалле уменьшают время разработки и стоимость готовых изделий. Также из-за усложнения фабрики FPGA, включая блоки памяти и блоки I/O, были разработаны более сложные алгоритмы синтеза, которые разделяют не связанные модули на части, уменьшая тем самым ошибки конечного размещения (post-placement).

Ядра интегрированных процессоров (IP Cores) предоставляются компанией Xilinx и другими сторонними производителями, чтобы можно было реализовать на системном уровне такие функции, как цифровая обработка сигналов (digital signal processing, DSP), интерфейсы различных стандартных шин, сетевые протоколы, обработку изображений, встраиваемые процессоры и периферийные устройства. У компании Xilinx есть инструментальные средства для перемещения ASIC-реализаций на аппаратные средства FPGA.

[Редакции Xilinx ISE]

Для загрузки доступны версии Subscription Edition, которая является лицензированной версией Xilinx ISE, также бесплатные trial-версии с ограниченным временем использования и версии с ограничениями функционала без ограничения срока действия.

Web Edition (ISE WebPack) является бесплатной версией Xilinx ISE, которую можно загрузить и использовать (для этого требуется регистрация на сайте Xilinx). Она дает возможность синтеза и программирования ограниченного количества устройств Xilinx. В частности, нельзя работать с устройствами, имеющими большое количество выводов I/O и большими матрицами элементов. Этой редакцией полностью поддерживаются недорогие семейства Spartan FPGA, а также семейство CPLD, таким образом небольшие компании и учебные организации могут использовать инструментарий разработки без дополнительных затрат.

Ниже в таблице приведена информация по поддержке микросхем Xilinx основными редакциями Xilinx ISE.

| ISE Webpack (free) | ISE Design Suite (commercial) | |

|---|---|---|

| Virtex FPGA | Virtex-4 LX: XC4VLX15, XC4VLX25 SX: XC4VSX25 FX: XC4VFX12 Virtex-5 Spartan-3A | |

| Coolrunner PLA Coolrunner-II CPLD Coolrunner-IIA CPLD | Все | |

| XC9500 Series CPLD | Все (кроме семейства 9500XV) | |

[Поддержка операционных систем]

Xilinx официально поддерживает Microsoft Windows, рабочие станции Red Hat Enterprise 4, 5 и 6 (32 и 64 бита) и SUSE Linux Enterprise 11 (32 и 64 бита). Некоторые другие дистрибутивы GNU/Linux могут запускать Xilinx ISE WebPack с некоторыми модификациями или дополнительным конфигурированием, включая Gentoo Linux, Arch Linux, FreeBSD и Fedora.

Далее рассмотрен процесс установки ISE WebPack и получение для него бесплатной лицензии по шагам.

1. Если у Вас еще нет учетной записи Xilinx, то зарегистрируйтесь. Это необходимо, потому что получение всех ссылок на закачку (и получение лицензий, даже бесплатных) происходит от имени зарегистрированного пользователя. Регистрация бесплатно доступна на сайте xilinx.com (пройдите по ссылке Sign In в верхней части главной страницы сайта).

3. Распакуйте архив в любую временную папку. Запустите cmd с правами системного администратора, и запустите в нем установщик xsetup.exe.

4. Когда установщик запросит вариант установки, выберите ISE WebPack. Этот вариант предусматривает получение бесплатной постоянной лицензии от Xilinx на большинство инструментов проектирования Xilinx. В процессе установки на все вопросы мастера отвечайте по умолчанию, пока не дойдет очередь до получения лицензии.

Примечание: во время установки будут установлены драйвера для USB-адаптеров программирования Xilinx, поэтому перед установкой убедитесь, что все адаптеры отключены от компьютера.

5. Когда установка завершится, запустится Xilinx License Configuration Manager. На первой закладке Acquire a License выберите вариант Get Free Vivado/ISE WebPack License и кликните Next. Запустится браузер, который (после ввода логина и пароля учетной записи Xilinx) откроет страничку Product Licensing. На первой закладке Create New Licenses, в разделе Certificate Based Licenses поставьте галочку на ISE WebPACK License, и нажмите на кнопку Generate Node-Locked License. Сгенерируется файл лицензии, и лицензию можно будет просмотреть на закладке Manage Licenses (в списке будет лицензия ISE WebPACK License).

7. Перейдите в окно Xilinx License Configuration Manager, откройте закладку Manage Licenses. Нажмите на кнопку Load License. и выберите присланный Вам файл лицензии Xilinx.lic. После этого список установленных лицензий обновится, и Вы сможете бесплатно пользоваться большинством возможностей Xilinx ISE WebPack.

Примечание: для пользователей WebPACK всегда активируется функция WebTalk. WebTalk игнорирует настройки пользователя и процедуры установки, когда генерируются конфигурационные данные программируемых схем логики (bitstream) под управлением лицензии WebPACK. Если Ваша разработка основана на устройстве, включенном в WebPACK, и доступна лицензия WebPACK, то всегда будет использоваться лицензия WebPACK. Чтобы изменить это, пожалуйста просмотрите Answer Record 34746.

1. Ссылку на закачку дистрибутива на сайте xilinx.com проще всего получить, если ввести строку поиска site:xilinx.com ISE WebPack Download. После перехода по ссылке сайт запросит ввести логин и пароль зарегистрированного пользователя (регистрация доступна бесплатно на том же сайте xilinx.com). Закачивайте Full Installer, размер файла примерно 6.5 гигабайт.

Закачанный файл это tar-архив, который в среде Windows можно распаковать с помощью Total Commander или архиватора 7Zip. Распакуйте содержимое архива в любую временную папку на диске.

2. В папке, которая распакована из архива, находится исполняемый файл xsetup.exe, запустите его.

Откроется мастер, который будет вести Вас по процессу установки. Ничего сложного, просто устанавливайте галочки, подтверждающие согласие с условиями лицензии, и кликайте на кнопку Next.

3. На следующем окне выберите для установки вариант ISE WebPack и кликните на кнопку Next.

4. Следующее окно предложит выбрать вариант установки лицензии и установку драйверов WinPCap и драйверов кабеля (это адаптер программирования микросхем Xilinx). Оставьте все галочки установленными по умолчанию и кликните Next.

5. Следующее окно предлагает выбрать каталог на диске, куда будет установлена система ISE WebPack, и выбор места для размещения ярлыков запуска.

Все предварительные установки выбраны, нажатие кнопки Install начнет установку:

Процесс установки долгий, может идти почти полчаса.

6. Для перехвата лицензионной информации, которая генерируется непосредственно на сайте Xilinx, инсталлятор использует драйвер WinPCap. Поэтому в процессе инсталляции будет установлен этот драйвер. Если на Вашем компьютере уже было ранее установлено программное обеспечение, использующее драйвер WinPCap, то может появиться сообщение о возможной проблеме совместимости.

Я выбрал «Запуск программы без получения справки», и успешно прошел все шаги установки драйвера WinPCap.

7. После установки драйвера WinPCap будет устанавливаться драйвер для JTAG-адаптеров программирования устройств Xilinx. Убедитесь, что на этом шаге у Вас отключены от компьютера адаптеры такого рода.

В этом окне кликните «Connect Now» (должно быть доступно подключение к Интернет), произойдет запуск браузера со страничкой диалога создания нового файла лицензии.

Выберите нужный вариант лицензии. Для бесплатной лицензии без ограничения срока действия нужно выбрать «ISE WebPack License», и кликнуть на кнопке «Generate Node-Locked Licence» (лицензия, действие которой привязано к рабочей станции).

На следующих двух окнах диалога (стадии просмотра лицензии 1, 2, 3, 4) просто кликните Next.

Сгенерируется файл лицензии Xilinx.lic.

Загрузите файл лицензии Xilinx.lic. Он будет доступен в папке «Загрузки».

Перейдите обратно в окно Xilinx License Configuration Manager. В этом окне нужно будет загрузить полученный файл лицензии.

Кликните на кнопку «Load License. » и выберите загруженный файл Xilinx.lic.

Менеджер подтвердит, что лицензия была успешно установлена:

9. После установки лицензии установка пакета ISE WebPack завершена.

Embedded System Solutions

Xilinx ISE 14.7 installation instructions for Windows 10

You must install Xilinx ISE 14.7 (October 2013) to target the Spartan-3A FPGA. It is available at:

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/design-tools/v2012_4—14_7.html

(Note: Xilinx ISE 14.7 from December 2017 does NOT support the Spartan-3A)

To run the October 2013 release on Windows 10: install as usual, then do the following:

1. Navigate to the following ISE install directory: \Xilinx\14.7\ISE_DS\ISE\lib\nt64\

2. Rename the file «libPortability.dll» to «libPortability.dll.orig».

3. Copy the «libPortabilityNOSH.dll» file to the same folder, and rename it to «libPortability.dll».

4. Repeat steps 1-3 in the following folder: \Xilinx\14.7\ISE_DS\common\lib\nt64\

The above steps substitute the original «libPortability.dll» with a «libPortability.dll» file that has SmartHeap disabled, the NOSmartHeap (NOSH) version. This does not negatively impact the operation of the tools, and should successfully work around the ISE 14.7 crash documented above.

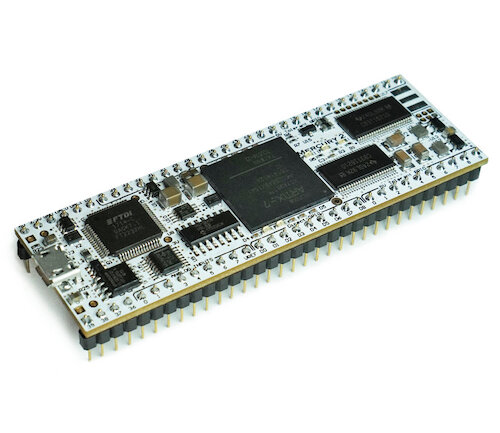

Our Mercury series of development boards pack a powerful Xilinx FPGA and supporting circuitry onto a compact, breadboard-friendly 3” x 1” DIP form-factor, providing a flexible platform for prototyping FPGA-based embedded systems. Mercury boards have been used worldwide by engineers, scientists, hobbyists and students to build awesome systems with FPGAs. Mercury boards are proudly manufactured in Metro Detroit, using our in-house SMT assembly line.

Как установить xilinx ise на windows 10

Часть 1. Установка Xilinx ISE WebPack

В этой статье хотелось бы осветить особенности и суть работы с САПР Xilinx ISE Design Suite. Номер версии советую выбирать последнюю из семейства ISE. Далее только Vivado поддерживающее 7+ поколение кристаллов Xilinx. В то время как ISE 14 поддерживает до 7 поколения включительно. Такое «пересечение» поддерживаемых версий дает возможность разработчикам плавно и безболезненно (теоретически) обновить свою САПР.

Xilinx ISE Design Suite начиная с 4 версии по своей сути мало чем менялась. В основе оставался все тот же синтезатор XST, который «подпиливался» с выходом очередного семейства микросхем, ну и конечно же устранялись ошибки. То же самое можно отметить и об интерфейсе. Тем не менее, шли годы, ISE Design Suite становилась лучше. И имеем мы на сегодняшний день 14 версию САПР вполне даже пригодную к серьезной работе.

Перед началом работы необходимо установить ISE Design Suite 14, скачав дистрибутив на сайте разработчика Xilinx. При этом можно сразу создать аккаунт на Xilinx.com, это потребуется при регистрации ISE Design Suite 14. Дистрибутив достаточно объемный порядка 6-8 Гб. Поэтому быстро скачать не удастся. После удачной закачки дистрибутива необходимо запустить установщик и следовать его указаниям.

Выбрать редакцию ISE WebPACK (бесплатная версия):

На экране настроек комплекта установки можно снять все снимаемые галки по желанию; галку «Install Cable Drivers» снять настоятельно рекомендуется:

Выбрать каталог для установки:

Проверить все заданные параметры перед установкой:

Сам процесс установки:

По завершению установки Вам будет предложено зарегистрировать установленный продукт. Вы регистрируете все на том же ресурсе разработчика ПО и получаете уникальный регистрационный (лицензионный) номер. Этот номер вы используете при первом запуске ISE WebPACK Design Software.

Полученный файл Xilinx.lic можно или сразу руками скопировать в домашний каталог в каталог:

Часть 2. Знакомство с интерфейсом

На рис.1 приведен интерфейс ISE Design. Рисунок я разделил на 4 основные области. Такой подход позволит качественно разобраться с назначением вкладок и разделов САПР. Начнем по порядку:

Рис.1. Интерфейс ISE WebPACK Design Software 14

Область #1 «Иерархия»

В этом окне отображается иерархия нашего проекта. Все модули, начиная с самого верхнего и заканчивая самым мелким глубоко спрятанных внутри можно посмотреть именно в этом окне. Из рисунка видно, что каждый блок (макрос) имеет собственный уникальный номер типа «XLXI_16» и наименование блока «BR_AK_4» см. рис 2. Так же здесь отображается

Рис.2. Иерархия проекта созданного в ISE WebPACK Design Software 14

наименование корневого каталога, в котором хранится наш проект. Чуть ниже указан тип кристалла, для которого создан наш проект, т.е. тип ПЛИС (FPGA). Следующим в иерархии стоит верхний (он помечен тремя квадратиками, верхний из которых зеленый) уровень проекта. И далее топовый (верхний) уровень проекта делится на свои составные части в зависимости от сложности.

Область #2 «Процессы»

Рис.3. Окно процессов в ISE WebPACK Design Software 14

Здесь располагаются основные узлы управления проектом: Отчеты, заданные ограничения, процессы синтеза, трассировки кристалла и т.д. Теперь подробнее о самых основных:

Думаю, это окно в особых комментариях не нуждается, все ясно из названия. Скажу лишь, что в этом окошке отображаются все информационные рабочие процессы (системные сообщения).

Область #4 «Общие сведения о проекте»

Таблицы, отражающие информацию об используемом кристалле, версии САПР ISE, наименование проекта, количество ошибок, предупреждений и т.п. Основной таблицей этого раздела является отчет о доступных и задействованных ресурсов выбранного кристалла.

Так же очень полезную информацию при наладке проекта можно узнать из таблицы детального отчета: Синтеза, Транслятора, Трассировщика, Временных задержек (очень важный параметр).

Вкладки, приведенные на рис. 4 так же помогают разработчику при работе с проектом, но интерфейс их интуитивно понятен и назначение их понятно из названия. Поэтому эти вкладки не будут рассмотрены подробно.

Рис.4. Дополнительные вкладки ISE WebPACK Design 14

Часть 3. Создание нового проекта

Рис.5. Создание нового проекта шаг #1.

Из рисунка видно, что предлагается заполнить 5 граф:

Далее кликаем кнопку «Next» и переходим в окно «Project Settings» (Задание настроек проекта) см. рис. 6.

Рис.6. Создание нового проекта шаг #2. Окно «Project Settings»

В этом окне выбираем семейство микросхем Xilinx “Spartan3E”,затем сам тип кристалла указываем “XC3S250E”. Задаем тип корпусного исполнения для выбранной микросхемы “PQ208” и её скорость “-4”. Все перечисленные величины можно найти на маркировке самой микросхемы.

Ниже указан тип топового уровня проекта – схемотехнический (см. рис. 5). Далее нам предлагается выбрать тип синтезатора, оставляем по умолчанию. Тут же можно указать симулятор, которым вы будете пользоваться при отладке (О нем я расскажу позже).

Кликаем кнопку «Next» и переходим в окно «Заданные настройки» (Заданные настроек проекта) см. рис. 7.

Рис.7. Заданные настройки шаг #3. Окно «Project Summary»

В этом окне можно проверить все то, что мы указали ранее.

Кликаем кнопку «Next» и видим пустой только что созданный проект см. рис. 8.

Рис.8. Пустой загрузившийся проект шаг #4.

Рис.9. Мастер создания нового описания (источника).

В открывшимся окне в графе “Select source type, file name and its location” необходимо выбрать вид представления вашего листа. То есть это может быть языки формального описания аппаратуры (Verilog или VHDL) или схемотехническое представление, либо генератор стандартных функций (IP CORE). Выберем самый наглядный и простой для начинающего схемотехнический вид “Schematic”. Правее в соответствующей графе указываем имя будущего описания и место его нахождения. Жмем на кнопку «Далее» и переходим в окно, показанное на рис. 10. Проверяем имя модуля, местоположение, тип представления.

Рис.10. Общие сведения о создаваемом модуле.