Что быстрее sram или dram

Универсальная память: SRAM, DRAM и флеш-память в одном флаконе

В наши дни существует не один вид памяти, каждый из которых применяется для той или иной задачи. Они со своими задачами справляются достаточно хорошо, но есть ряд недостатков, которые не дают возможность назвать какой-либо из этих вариантов памяти универсальным. Если добавить сюда проблему колоссального роста данных во всем мире и жажду человечества к энергосбережению, то необходимо создать что-то совершенно новое. Сегодня мы познакомимся с исследованием, в котором ученые представили новый тип памяти, объединяющий в себе достоинства как флеш, так и DRAM памяти. Какими «плюшками» обладает данное новшество, какие технологии были задействованы для его создания и какие перспективы? Об этом мы узнаем из доклада исследовательской группы. Поехали.

Основа исследования

Типов памяти существует далеко не один, и все они были созданы для конкретной задачи: SRAM (статическая память с произвольным доступом) для кеша, DRAM (динамическая память с произвольным доступом) для активной памяти, флеш-память для хранения данных и т.д. Однако, что вполне ожидаемо, у каждого из вышеперечисленных типов памяти есть свои персональные недостатки.

Например, флеш-память, представляющая собой совокупность МОП-транзисторов (металл-оксид-полупроводник) с плавающим затвором (FG) для хранения заряда. Данные представлены в таком варианте как количество заряда, удерживаемого в FG, который изолирован оксидными слоями.

Несмотря на этот минус, есть достаточно внушительный плюс — считывание данных происходит посредством проверки проводимости канала, для чего нужно совсем небольшое напряжение. Благодаря этому данные остаются нетронутыми, что называют неразрушающим считыванием.

DRAM, в свою очередь, значительно быстрее флеш-памяти, потому и используется для активных вычислительных процессов, так сказать. Недостаток DRAM в том, что данные теряются из ячеек при считывании. Помимо этого возникают утечки заряда из конденсаторов, используемых для хранения данных.

SRAM также достаточно быстрый тип памяти и данные не так теряются, как в DRAM. Однако, как правило, используется по 6 транзисторов на ячейку, то есть нужно много площади на чипе.

Представив вышеописанные недостатки классических типов памяти, ученые подчеркивают важность поиска альтернативного или гибридного варианта, который будет лишен подобных проблем, при этом совместит в себе все преимущества своих предшественников.

В данном труде исследователи представляют нашему вниманию свое видение нового типа памяти — нового низковольтного, полупроводникового, основанного на заряде, энергонезависимого запоминающего устройства компактной формы, работающего при комнатных температурах. Исследователи окрестили свое детище «универсальной памятью» (простенько, но со вкусом).

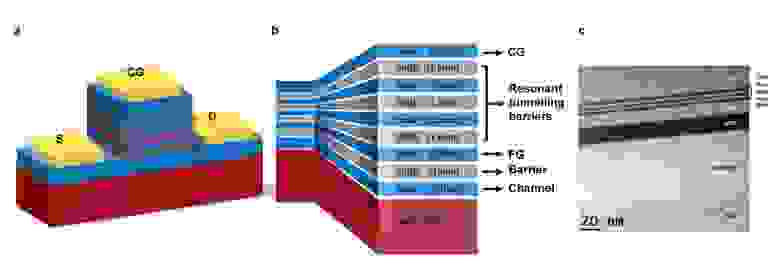

Устройство представляет собой память с плавающим затвором, созданную на базе гетероструктур InAs/AlSb/GaSb, где InAs применяется и как плавающий затвор, и как канал без переходов.

Ученые предоставили результаты моделирования и фактических испытаний прототипа с одной ячейкой.

Результаты исследования

Изображение №1

На изображении выше представлены схематический вид устройства и снимок ПРЭМ (просвечивающего растрового электронного микроскопа).

Как и в случае флеш-памяти, в данном устройстве заряд хранится в FG, но при этом отсутствуют оксидные барьеры. Вместо этого было использовано смещение зоны проводимости в так называемом 6.1-Å семействе полупроводников. То есть устройство, лежащее в основе ячейки памяти, больше похоже на транзистор с высокой подвижностью электронов (HEMT), чем на МОП-транзистор. InAs образует канал, который не содержит переходов. Однако было применено n-легирование, дабы компенсировать непреднамеренное фоновое легирование и удержать Ga вакансии в нижележащем GaSb. Обе эти задачи естественным образом делают слои p-типа.

p-n-переход* — участок соприкосновения двух полупроводников с разными типами проводимости — p (дырочной) и n (электронной).

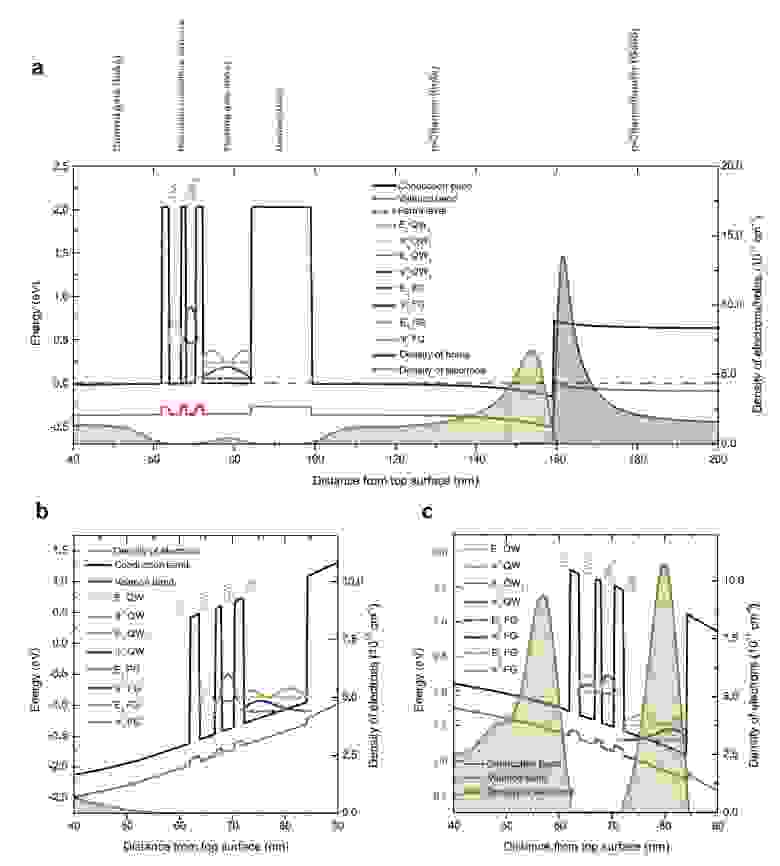

Изображение №2

График 2а демонстрирует смоделированное выравнивание энергетических зон, а также плотность электронов и дырок в слоях при отсутствии смещения. Теоретические данные в совокупности с моделированием демонстрируют, что на интерфейсе InAs и GaSb зона проводимости InAs находится ниже валентной зоны GaSb. А это приводит к перемещению электронов из слоя GaSb в слой InAs, после чего в GaSb остаются дырки.

Дырка* — незаполненная валентная связь, проявляющая себя как положительный заряд, равный заряду электрона.

Накопленные электроны/дырки видны на границе между InAs и GaSb, но электроны в канале InAs не связаны с интерфейсом InAs / GaSb, при этом их плотность наблюдается по всему InAs. В проводимости всего канала преобладают электроны в InAs, которые будут иметь более высокую подвижность и более высокую плотность, чем дырки в GaSb.

Внутренний FG слоя InAs изолирован от канала InAs барьером AlSb (15 нм). В то же время, двойные квантовые ямы* InAs и три барьера AlSb выполняют роль резонансно-туннельного барьера между FG и CG InAs с n-легированием.

Квантовая яма* — ограничивает движение частиц в двумерном измерении (вместо трехмерного), из-за чего они могут двигаться только в плоском слое.

Следовательно, в исследуемом устройстве электроны, хранящиеся в FG слоя InAs, изолированы аномально большим разрывом зоны проводимости с AlSb. Это значит, что можно получить систему ограничения заряда, которая будет иметь время хранения при комнатной температуре, равное 1014 лет.

Самым важным аспектом работы исследуемого устройства является факт того, что две квантовые ямы (QW1 и QW2) в тройном резонансно-туннельном барьере имеют разные толщины, то есть имеют место ограниченные состояния с разными энергиями (2a). Поскольку QW2 тоньше QW1, единственный доступный уровень энергии для электронов в QW2 имеет более высокую энергию, чем эквивалент в QW1. Кроме того, состояние в QW1 имеет значительно более высокую энергию, чем состояние в соседнем CG участке. Таким образом предотвращается прямое туннелирование электронов между CG и FG, а барьер перехода электронов из CG в FG (или наоборот) определяется смещением зоны проводимости InAs / AlSb на 2,1 эВ, то есть заряд не будет течь к/от FG.

Основное и первичное возбужденное состояния в плавающем затворе (FG) расположены значительно ниже энергетических состояний внутри обеих QW. Следовательно, когда не применяется никакого напряжения, электроны заперты внутри FG, т.е. тройной резонансно-туннельный барьер становится непреодолимым для электронов в/из FG. Таким образом достигается энергонезависимость.

Если же применить незначительное напряжение к управляющему затвору (CG), то можно настроить связь энергетических состояний внутри резонансного туннельного барьера, что позволит электронам свободно проходить из (2b) или в (2с) плавающий затвор.

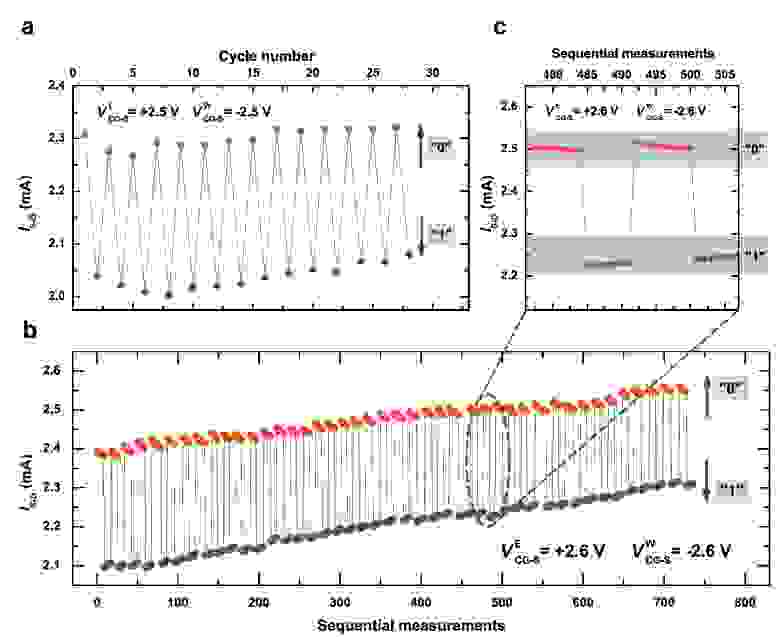

Во время экспериментов все операции чтения, записи и стирания проводились в нескольких ячейках (размер затвора — 10 х 10 мкм) в защищенном от электростатики темном боксе при комнатной температуре. Все операции, включая записи и стирание, выполнялись при смещении ≤ 2,6 В, что примерно на порядок ниже, чем необходимо для полноценной работы с ячейкой флеш-памяти, подчеркивают исследователи. Стирание выполнялось путем смещения управляющего затвора (V E CG-S) на +2.5 или +2.6 В между CG и источником, что приводило к состоянию «0».

График 2с это смоделированная энергетическая зона, когда для записи данных используется смещение управляющего затвора: V W CG-S = −2.6 В. В этом случае энергетические уровни в QW1 и QW2 практически совпадают, что приводит к сильной связи этих состояний, резонансному туннелированию и потоку электронов из CG в FG.

Из-за емкостной связи проводимость канала зависит от количества заряда, хранящегося в FG, поэтому чтение данных осуществляется посредством измерения тока затвор-исток при фиксированном напряжении затвор-исток.

Повышение заряда в FG, т.е. состояние «1», уменьшает заряд в канале, что приводит к снижению его проводимости. В случае состояния «0» происходит обратный процесс. Считывание данных можно осуществить и без какого-либо смещения к CG, но напряжение необходимо для индивидуальной выборки устройств в массиве ячеек. Кроме того, напряжение должно генерировать электрическое поле по резонансно-туннельному барьеру, что сделает возможным переход заряда из/в FG. Для достижения этих задач потребуется всего лишь

Характеристики универсальной памяти

Во время практических испытаний чтение было выполнено с нулевым смещением на CG и VS-D = 1.0 В. Однако, по заявлениям ученых, можно было применить и меньшее напряжение для успешного чтения.

Изображение №3

На изображении 3а показана последовательность операций стирание-чтение-запись-чтение. Главной особенностью последовательности является операция чтения после каждого шага стирания или записи.

На изображении 3b показана более усложненная последовательность, в которой после каждой операции стирания и записи идет не одна операция чтения, а несколько. Таким образом исследователи демонстрируют то, что операция чтения имеет неразрушающий характер.

Между состоянием «0» и «1» наблюдается четкое отличие во всех последовательностях. Однако на 3b имеются признаки симметричного восходящего сдвига в IS-D по мере увеличения числа операций. Пока причина такого поведения неясна, но ученые намерены исследовать этот аспект в дальнейших трудах. А вот на 3а такого не наблюдается, поскольку напряжение для стирания/записи немного ниже.

После нескольких сотен операций записи и стирания, а также множества операций чтения во время нескольких тестовых практических испытаний ученые не обнаружили никаких признаков повреждения устройства.

Важной особенностью всех типов памяти, которые основаны на хранении заряда, является энергия переключения, определяемая зарядной энергией конденсатора.

Сходство фундаментальных основ технологии флеш-памяти и исследуемой универсальной памяти наталкивает на сравнение этих двух типов памяти. Если предположить, что у двух устройств этих двух типов одинаковая емкость при одинаковом размере затвора, то энергия переключения универсальной памяти будет в 64 раза меньше, чем у флеш-памяти. Эти удивительные цифры также говорят о превосходстве универсальной памяти и над DRAM.

На изображении 3с показаны некоторые операции записи-стирания из 3b, где видны отличия состоянии «0» и «1»: последовательные измерения чтения после стирания дают немного меньший IS-D для состояния «0». Противоположная ситуация наблюдается при последовательных измерениях чтения после записи, а точнее IS-D немного больше.

Данный эффект ученые связывают с изменчивостью (волатильностью) данных. Для изучения этого ученые выполнили последовательность операции чтения в течение длительного периода времени для каждого состояния памяти (изображение №4).

Изображение №4

Оба состояния «0» и «1» демонстрировали начальное быстрое затухание, которое согласуется с тем, что видно на 3с. Но после этого происходят гораздо более медленные изменения, так что в течение всего времени наблюдения соответствующие состояния «0» и «1» четко различимы.

Также был проведен еще один эксперимент (вставка на изображении №4), который показывает предельное насыщение экспоненциальных затуханий и различимых состояний «0» и «1» во времени.

Существование двойного экспоненциального затухания означает, что в основе деградации состояний лежат сразу несколько механизмов. Среди возможных вариантов ученые выделяют туннелирование через дефектные состояния в барьерах AlSb, тепловое возбуждение электронов через узкую запрещенную зону InAs и рекомбинацию с термически генерируемыми дырками.

Оценка емкости устройства и примененного напряжения для записи/стирания говорит о том, что во время операции записи и стирания из/в плавающий затвор переносится примерно 107 электронов. Это достаточно много, но негативного влияния практически не наблюдается.

Для более детального ознакомления с нюансами исследования рекомендую заглянуть в доклад исследовательской группы.

Эпилог

Ученым удалось не только разработать новый тип памяти, но и провести успешные первые практические испытания энергонезависимого, основанного на заряде устройства компактного размера при комнатной температуре. Ученым также удалось совместить энергонезависимость и низковольтное переключение путем квантово-механических свойств асимметричного тройного резонансно-туннельного барьера. Исследователи заявляют, что их устройство можно масштабировать, при этом не теряя его достоинства.

Времена меняются, меняются и технологии. Флеш-память, SRAM и DRAM достаточно долго занимали господствующее положение среди устройств памяти, однако это может измениться, если разработка универсальной памяти продолжится с таким же успехом, как и в данном исследовании. Данная технология позволит сильно сократить энергопотребление устройств, оснащенных ею, а также продлить их срок службы и повысить производительность.

Дальнейшие исследования, запланированные авторами, покажут насколько революционной является память, столь гордо названная учеными универсальной.

Благодарю за внимание, оставайтесь любопытствующими и хорошей всем рабочей недели, ребята!

Разница между статической и динамической памятью, которая быстрее? 2019

ОЗУ (оперативное запоминающее устройство) — это разновидность памяти, которая требует постоянной мощности для сохранения данных в ней; после сбоя источника питания данные будут потеряны, поэтому она известна как энергозависимая память. Существует два типа статического ОЗУ с оперативной памятью (ОЗУ) и динамического ОЗУ, каждый из которых имеет свои преимущества и недостатки по сравнению с другим. Здесь полное руководство в чем разница между срамом и драмом, Какой из них лучше SRAM и DRAM, почему DRAM нужно обновлять тысячи раз?

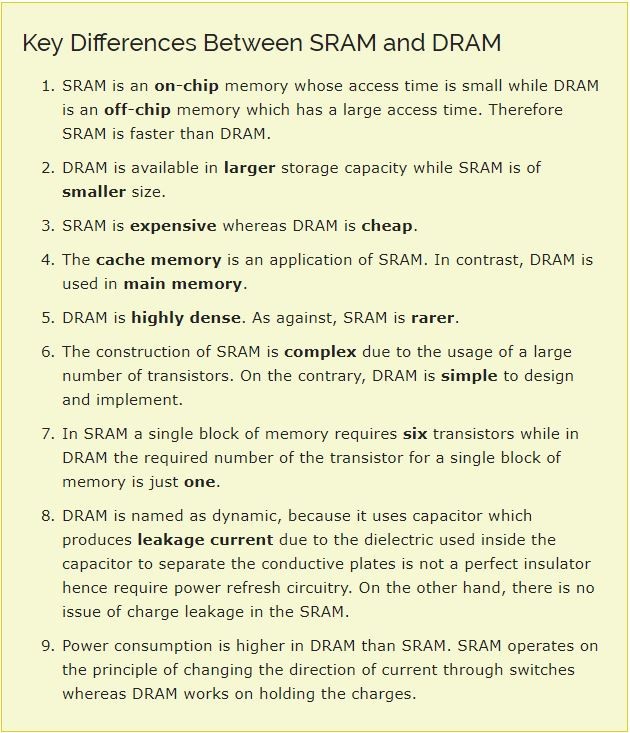

Разница между SRAM и DRAM

Статическая ОЗУ и динамическая ОЗУ отличаются друг от друга во многих контекстах, таких как скорость, емкость и т. Д. Эти различия возникают из-за различий в технике, используемой для хранения данных. DRAM использует один транзистор и конденсатор для каждой ячейки памяти, в то время как каждая ячейка памяти SRAM использует массив из 6 транзисторов. DRAM нуждается в обновлении, тогда как SRAM не требует обновления ячейки памяти.

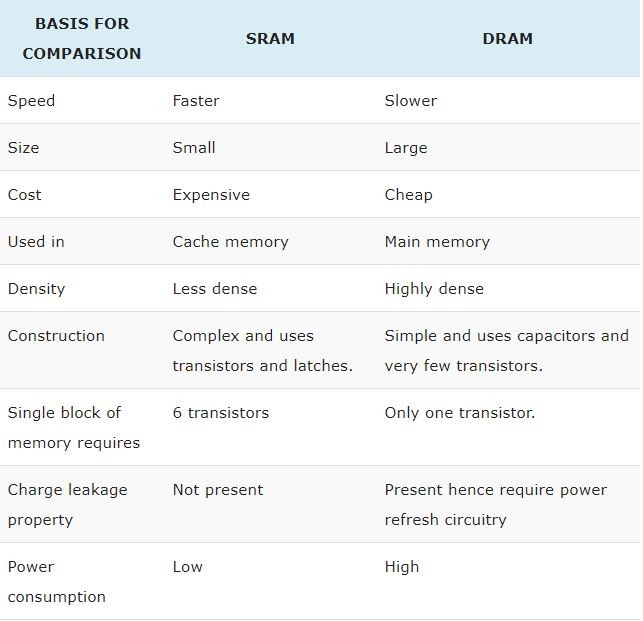

Срам против диаграммы сравнения драма

Динамическая RAM

Статическая RAM

определение драм и драм

DRAM обозначает динамическую оперативную память это широко используется в качестве основной памяти для компьютерной системы. DRAM требует 1 транзистор и 1 конденсатор для хранения 1 бита. Средство Каждая ячейка памяти в микросхеме DRAM содержит один бит данных и состоит из транзистора и конденсатора. Транзистор функционирует как переключатель, который позволяет схеме управления на микросхеме памяти считывать конденсатор или изменять его состояние, в то время как конденсатор отвечает за удержание бита данных в форме 1 или 0.

Как мы знаем, конденсатор похож на контейнер, в котором хранятся электроны. Когда этот контейнер заполнен, он обозначает 1, в то время как контейнер, пустой электронов, обозначает 0. Однако конденсаторы имеют утечку, которая приводит к тому, что они теряют этот заряд, и в результате «контейнер» становится пустым через несколько секунд. миллисекунды. И чтобы чип DRAM работал, процессор или контроллер памяти должны перезарядить конденсаторы, которые заполнены электронами (и, следовательно, указать 1), прежде чем они разрядятся, чтобы сохранить данные. Для этого контроллер памяти считывает данные и затем переписывает их. Это называется обновлением и происходит тысячи раз в секунду в микросхеме DRAM. Из-за необходимости постоянно обновлять данные, что занимает много времени, DRAM работает медленнее.

Наиболее распространенным применением DRAM, таким как DDR3, является энергозависимое хранилище для компьютеров. Хотя DRAM не такой быстрый, как SRAM, он по-прежнему очень быстрый и может подключаться непосредственно к шине ЦП. Типичные размеры DRAM составляют от 1 до 2 ГБ для смартфонов и планшетов и от 4 до 16 ГБ для ноутбуков.

SRAM обозначает статическую оперативную память, Обычно он используется для создания очень быстрой памяти, известной как кэш-память. SRAM требует 6 транзисторов для хранения 1 бита, и это намного быстрее по сравнению с DRAM. Статическая RAM использует совершенно другую технологию по сравнению с DRAM. В статической оперативной памяти форма триггера содержит каждый бит памяти. Триггер для ячейки памяти требует 4 или 6 транзисторов вместе с некоторой разводкой, но не требует обновления. Это делает статическое ОЗУ значительно быстрее, чем динамическое. В отличие от динамического ОЗУ (DRAM), которое хранит биты в ячейках, состоящих из конденсатора и транзистора, SRAM не требует периодического обновления.

Однако из-за того, что он содержит больше частей, ячейка статической памяти занимает на чипе намного больше места, чем ячейка динамической памяти. Таким образом, вы получаете меньше памяти на чип, и это делает статическую память намного дороже.

Это быстрее: Поскольку SRAM не нужно обновлять, обычно это происходит быстрее. Среднее время доступа DRAM составляет около 60 наносекунд, а SRAM может дать время доступа всего 10 наносекунд.

Наиболее распространенным применением SRAM является кэш-память процессора (CPU). В спецификациях процессора это указано как кэш-память второго уровня или кэш-память третьего уровня. Производительность SRAM действительно высокая, но SRAM дорогая, поэтому типичные значения кэша L2 и L3 составляют от 1 до 8 МБ.

статический баран против динамического баран

Основное различие между ними заключается в технологии, которая используется для хранения данных. Из-за этого ключевого различия возникают и другие различия. SRAM использует защелки для хранения данных (транзисторная схема), тогда как DRAM использует конденсаторы для хранения битов в виде заряда. SRAM использует обычную высокоскоростную технологию CMOS для строительства, тогда как DRAM использует специальные процессы DRAM для достижения оптимизированной высокой плотности. Динамические RAM имеют более простую внутреннюю структуру, чем SRAM.

Срам против скорости драма

SRAM обычно быстрее, чем DRAM так как у него нет циклов обновления. Поскольку каждая ячейка памяти SRAM состоит из 6 транзисторов, в отличие от ячейки памяти DRAM, которая состоит из 1 транзистора и 1 конденсатора, стоимость одной ячейки памяти в SRAM намного выше по сравнению с DRAM.

Я надеюсь, что теперь вы, возможно, поняли разницу между SRAM и DRAM. И что немаловажно, причина необходимости обновления ОЗУ сотню раз за такт. Тем не менее есть какие-либо вопросы запроса, не стесняйтесь обсуждать комментарии.

Разница между SRAM и DRAM

главное отличие между RAM и DRAM в том, что RAM не требует циклов обновления для хранения данных, в то время как DRAM требует периодических циклов обновления для сохранения данных. Процессору требует

Содержание:

главное отличие между SRAM и DRAM в том, что SRAM не требует циклов обновления для хранения данных, в то время как DRAM требует периодических циклов обновления для сохранения данных.

Процессору требуется больше времени для доступа к жесткому диску. Следовательно, выполняющиеся процессы помещаются в основную память или оперативную память. Оперативная память позволяет получать доступ к данным быстрее, чем к носителям, таким как жесткие диски, твердотельные накопители. Он обозначает произвольную память. Объем ОЗУ определяет, насколько быстро работает устройство. Это энергозависимая память, для поддержания данных в оперативной памяти требуется постоянный ток. Поэтому при отключении тока содержимое в ОЗУ будет удалено. Существует два типа оперативной памяти: SRAM (статическая RAM) и DRAM (динамическая RAM). Разница между ними заключается в требовании цикла обновления.

Ключевые области покрыты

1. Что такое SRAM

— определение, функциональность

2. Что такое ДРАМ

— определение, функциональность

3. Разница между SRAM и DRAM

— Сравнение основных различий

Основные условия

SRAM, DRAM, операционная система

Что такое SRAM

Рисунок 1: Ячейка SRAM

SRAM используется для маршрутизаторов персональных компьютеров, периферийных устройств, кэш-памяти ЦП, файлов регистров и т. Д. Он также используется в промышленных и научных подсистемах и автомобильной электронике, которая требует высокой производительности. В целом, SRAM быстр и надежен, но стоит дороже.

Что такое ДРАМ

DRAM означает Динамическая Оперативная Память, Это полупроводниковая память, которая хранит каждый бит в отдельном конденсаторе с интегральной схемой. Конденсатор может заряжаться или разряжаться и представляет собой логический единица и логический ноль. Существует некоторый ток утечки, и конденсатор потеряет заряд. Это может стереть данные на чипе. Чтобы избежать этой проблемы, DRAM должен использовать схему обновления. Эта схема постоянно перезаписывает данные в конденсаторе и восстанавливает их первоначальный заряд. Поэтому память DRAM является динамической и требует непрерывных циклов обновления для сохранения данных.

Рисунок 2: DRMA

В целом, DRAM не так быстр, как SRAM, но он быстрее, чем другие компоненты хранения, такие как жесткий диск. Это наиболее распространенный тип основной памяти, и он не такой дорогой, как SRAM. Он часто используется для приложений цифровой электроники, которые требуют низкой стоимости и большой емкости памяти.

Разница между SRAM и DRAM

Определение

Стенды для

SRAM обозначает статическую память с произвольным доступом. DRAM означает динамическое оперативное запоминающее устройство.

скорость

SRAM очень быстро. DRAM быстрее, чем вторичное хранилище, такое как жесткий диск, но не так быстро, как SRAM.

Обновить циклы

Кроме того, SRAM не требует циклов обновления для сохранения данных. DRAM требует периодических циклов обновления для сохранения данных.

Аппаратная сложность

Поскольку DRAM требует обновления, он имеет более сложные требования к схемам и синхронизации по сравнению с SRAM.

использование

Время доступа

Кроме того, SRAM требует минимального времени для доступа к данным. DRAM требует больше времени для доступа к данным, чем SRAM.

Потребляемая мощность

SRAM потребляет меньше энергии, чем DRAM на низких частотах. Это становится сопоставимым на более высоких частотах.

Структура ячейки памяти

Структура SRAM сложна. У него есть шлепки. С другой стороны, структура DRAM проста. У него есть транзистор и конденсатор.

плотность

Плотность относится к числу ячеек памяти на единицу площади. SRAM имеет более низкую плотность по сравнению с DRAM.

Стоимость

SRAM дороже, чем DRAM.

Заключение

Ссылка:

1. «Статическая память с произвольным доступом». Википедия, Фонд Викимедиа, 10 июля 2018 г.