дешифратор двоичного кода в десятичный

Декодеры

Декодеры позволяют преобразовывать одни виды двоичных кодов в другие. Например, преобразовывать двоичный код в линейный восьмеричный или шестнадцатеричный. Преобразование производится по правилам, описанным в таблицах истинности, поэтому построение дешифраторов не представляет трудностей. Для построения дешифратора можно воспользоваться правилами синтеза логической схемы для произвольной таблицы истинности.

Десятичный декодер

Рассмотрим пример разработки декодера двоичного кода в десятичный. Десятичный код обычно отображается одним битом на одну десятичную цифру. Это классический пример, иллюстрирующий, что нулями и единицами описываются не только двоичные коды. В десятичном коде десять цифр, поэтому для отображения одного десятичного разряда требуется десять выходов дешифратора. Около каждого разряда десятичного кода может быть подписана десятичная цифра, которую представляет логическая единица в этом разряде. Сигнал с этих выводов дешифратора можно подать на десятичный индикатор. В простейшем случае над светодиодом можно просто подписать индицируемую цифру. В более сложных вариантах индикатор можно выполнить в виде десятичной цифры.

На входе дешифратора двоичный код записывается в соответствии с правилами двоичной системы счисления. Таблица истинности десятичного декодера приведена в таблице 1.

Таблица 1. Таблица истинности десятичного декодера.

| Входы | Выходы | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 8 | 4 | 2 | 1 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

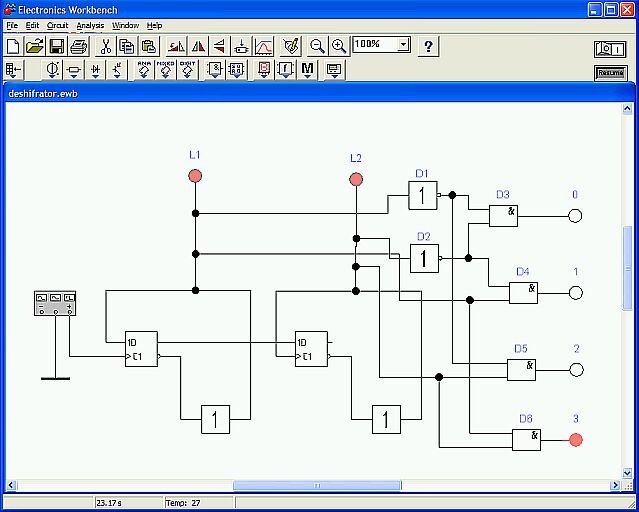

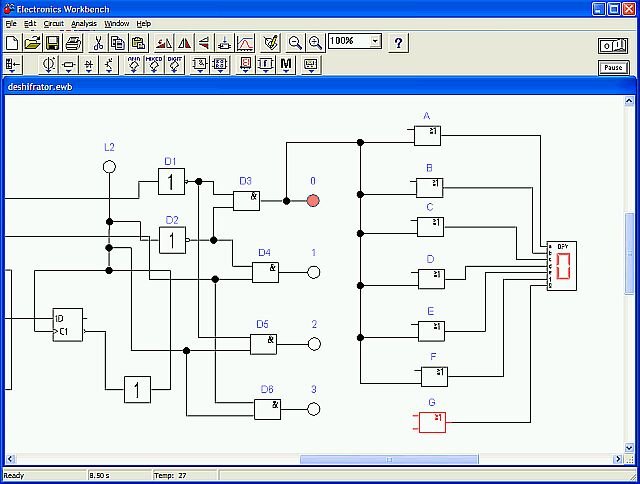

В соответствии с принципами построения схемы по произвольной таблице истинности получим схему декодера, реализующего таблицу истинности, приведённую в таблице 1. Его схема приведена на рисунке 1.

Рисунок 1. Принципиальная схема двоично-десятичного декодера

Как видно на этой схеме, для реализации каждой строки таблицы истинности (минтерма) потребовался логический элемент «4И». Логический элемент «ИЛИ», необходимый для реализации СДНФ, не потребовался, так как в таблице истинности на каждом выходе (столбце) присутствует только одна логическая единица.

Двоичные декодеры выпускаются в виде отдельных микросхем или используются в составе других микросхем. В настоящее время десятичные или восьмеричные дешифраторы используются в основном как составная часть других микросхем, таких как мультиплексоры, демультиплексоры, ПЗУ или ОЗУ.

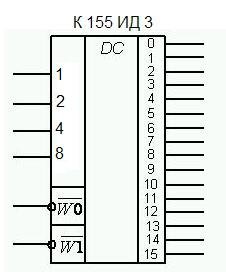

Условно-графическое обозначение микросхемы дешифратора на принципиальных схемах приведено на рисунке 2. На этом рисунке приведено обозначение двоично-десятичного декодера, полная внутренняя принципиальная схема которого изображена на рисунке 1.

Рисунок 2. Условно-графическое обозначение десятичного декодера

Точно таким же образом можно получить принципиальную схему и для любого другого декодера. Наиболее распространены схемы восьмеричных и шестнадцатеричных декодеров. Для применения в схемах индикации в настоящее время они практически не используются. В основном такие, или более сложные (с большим количеством выходов) декодены используются как составная часть более сложных цифровых модулей.

Семисегментный декодер

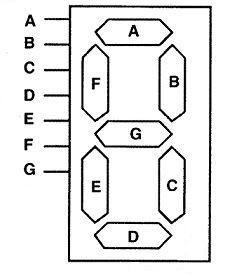

Для отображения десятичных и шестнадцатеричных цифр часто используется семисегментный индикатор. Внешний вид семисегментного индикатора и название его сегментов приведено на рисунке 3.

Рисунок 3. Внешний вид семисегментного индикатора и название его сегментов

Для отображения на таком индикаторе цифры 0 достаточно зажечь сегменты a, b, c, d, e, f. Для отображения цифры ‘1’ зажигают сегменты b и c. Точно таким же образом можно получить изображения всех остальных десятичных или шестнадцатеричных цифр. Все комбинации двоичных бит, необходимых для получения их изображений получили название семисегментного кода.

Составим таблицу истинности дешифратора, который позволит преобразовывать двоичный код в семисегментный. Пусть сегменты зажигаются нулевым потенциалом. Тогда таблица истинности семисегментного дешифратора примет вид, приведенный в таблице 2. Конкретное значение сигналов на выходе дешифратора зависит от схемы подключения сегментов индикатора к выходу микросхемы. Эти схемы мы рассмотрим позднее, в главе, посвящённой отображению различных видов информации.

Таблица 2. Таблица истинности семисегментного декодера.

| Входы | Выходы | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 8 | 4 | 2 | 1 | a | b | c | d | e | f | g |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

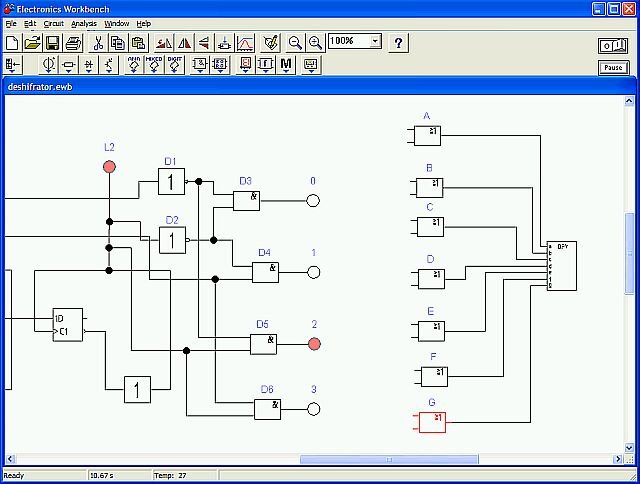

В соответствии с принципами построения схемы по произвольной таблицы истинности, получим принципиальную схему семисегментного декодера, реализующего таблицу истинности, приведённую в таблице 2. На этот раз не будем подробно расписывать процесс разработки схемы. Полученная принципиальная схема семисегментного декодера приведена на рисунке 4.

Рисунок 4. Принципиальная схема семисегментного декодера

Для облегчения понимания принципов работы схемы на выходе логических элементов «И» показаны номера строк таблицы истинности, реализуемые ими.

Например, на выходе сегмента ‘a’ логическая единица появится только при подаче на вход комбинации двоичных сигналов 0001 (1) и 0100 (4). Это осуществляется объединением соответствующий цепей элементом «2ИЛИ». На выходе сегмента ‘b’ логическая единица появится только при подаче на вход комбинации двоичных сигналов 0101 (5) и 0110 (6), и так далее.

В настоящее время семисегментные дешифраторы выпускаются в виде отдельных микросхем или используются в виде готовых блоков составе других микросхем. Условно-графическое обозначение микросхемы семисегментного дешифратора приведено на рисунке 5.

Рисунок 5. Условно-графическое обозначение семисегментного декодера

В качестве примера промышленного производства семисегментных декодеров можно назвать такие микросхемы отечественного производства как К176ИД3. В современных цифровых схемах семисегментные дешифраторы обычно входят в состав больших интегральных схем (ПЛИС или FPGA) или реализуются программно.

Понравился материал? Поделись с друзьями!

Вместе со статьей «Дешифраторы (декодеры)» читают:

Законы алгебры логики Законы алгебры логики позволяют преобразовывать логические функции. Логические функции преобразуются с целью их упрощения, а это ведет к упрощению цифровой схемы.

https://digteh.ru/digital/AlgLog.php

Синтез цифровых комбинационных схем по произвольной таблице истинности Для реализации цифровых логических схем с произвольной таблицей истинности используется сочетание простейших логических элементов. Существует два способа синтеза цифровых схем, реализующих произвольную таблицу истинности.

https://digteh.ru/digital/SintSxem.php

Шифраторы (кодеры) Достаточно часто перед разработчиками цифровой аппаратуры встаёт обратная задача. Требуется преобразовать восьмиричный или десятичный линейный код в.

https://digteh.ru/digital/Coder.php

Мультиплексоры Мультиплексорами называются устройства, которые позволяют подключать несколько входов к одному выходу.

https://digteh.ru/digital/MS.php

Демультиплексоры Демультиплексорами называются устройства. Существенным отличием от мультиплексора является.

https://digteh.ru/digital/DMS.php

Дешифратор двоичного кода в десятичный

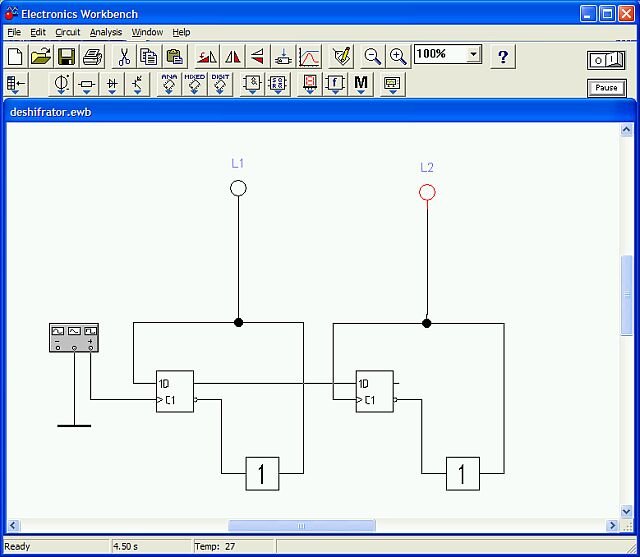

Выходы каждого триггера подключены индикаторы L1 и L2. Если включить схему и наблюдать переключение индикаторов, то можно выявить некоторую упорядоченную последовательность их переключения. Опишем эту последовательность в виде таблицы. Свечение индикатора будет состоянием 1, а отсутствие свечения будет состоянием 0.

Мы видим, сто делитель создаёт определённый код, которому можно поставить в соответствие десятичные значения (Этот код называется позиционным двоичным кодом 1-2-4-8). Попробуем собрать схему, которая будет преобразовывать двоичный код в десятичный, а десятичные значения будем отображать соответствующими индикаторами.

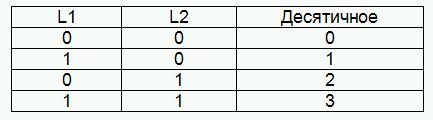

Сначала создадим логическую схему, которая при двоичном состоянии 0-0 будет отображать 0. Нам понадобятся два элемента NOT (D1 и D2) и один AND (D3).

Если вход элемента D1 подключить к индикатору L1, а вход элемента D2 подключить к индикатору L2, то при состоянии 0-0 на индикаторах, на выходах элементов D1 и D2 будет состояние 1-1.

Выходы элементов D1 и D2 подключены к элементу D3 (AND), следовательно, на выходе элемента будет состояние 1 и индикатор 0 будет гореть. Как только состояние на индикаторах L1 и L2 изменится, индикатор 0 погаснет.

Продолжим развивать схему и сделаем ещё один индикатор, отображающий десятичную единицу. Для этого потребуется ещё один элемент AND (D4). Включим его как показано на рисунке.

В этом случае один вход элемента AND подключен непосредственно к индикатору L1, а второй вход элемента AND подключен к выходу элемента NOT (D2), который подключен к индикатору L2. Когда на индикаторе L1 будет присутствовать 1, а на индикаторе L2 будет присутствовать 0, то элемент AND (D4) сработает и индикатор 1 загорится.

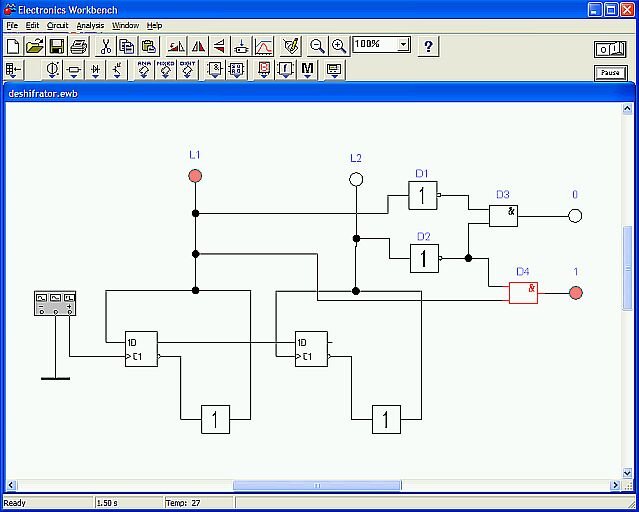

Далее, добавим индикатор 2. Для этого понадобится ещё один элемент AND (D5).

Следуя логике предыдущих рассуждений, подключим один вход элемента D5 непосредственно к индикатору L2, а второй вход к выходу элемента D1. Теперь индикатор 2 будет загораться только в том случае, если на индикаторе L2 будет состояние 1, а на индикаторе L1 состояние 0.

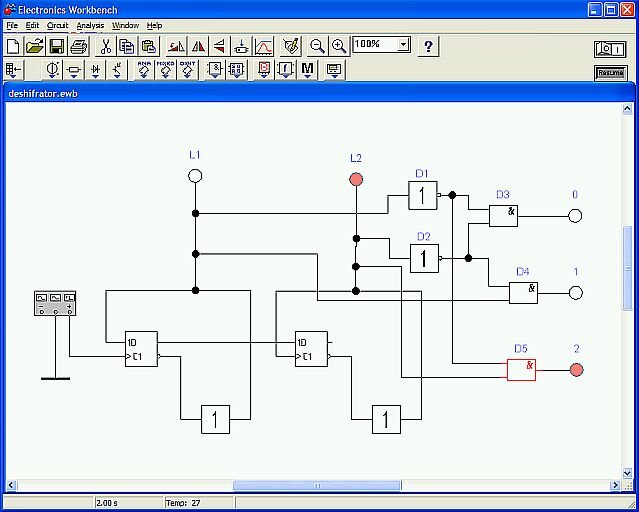

И, наконец, создадим индикатор 3. Здесь всё очень просто, когда на индикаторах L1 и L2 присутствует 1, то индикатор 3 должен гореть. Подключим элемент AND (D6) непосредственно к индикаторам.

Семисегментный дешифратор Недостаток нашей схемы заключается в том, что при отображении числа, например 200, нам потребуется 200 индикаторных лампочек или светодиодов. В реальной жизни, обычно используют так называемые цифровые семисегментные индикаторы.

Семисегментный индикатор состоит из 7 элементов, которые могут при подаче на них напряжения (состояние 1) светиться или изменять свой цвет. Типовой Семисегментный индикатор показан на рисунке:

Каждый сегмент имеет электрический контакт для подключения в схему. Рассмотрим, что нужно сделать, что бы подключить такой индикатор к нашему десятичному дешифратору.

Для включения цифры 0 следует подать сигнал 1 на выводы (контакты) A, B, C, D, E и F.

Для включения цифры 1 следует подать сигнал 1 на выводы B и C.

Для включения цифры 2 следует подать сигнал 1 на выводы A, B, G, E и D.

Для включения цифры 3 следует подать сигнал 1 на выводы A, B, G, C и D.

Для создания очередного дешифратора воспользуемся многовходовыми логическими элементами ИЛИ (OR). Расположим на схеме семисегментный индикатор и 7 логических элементов ИЛИ. Соединим выходы логических элементов с входами семисегментного индикатора.

Соединим индикатор 0 с соответствующими входами элементов ИЛИ. Включим питание и убедимся, что 0 отображается на семисегментном индикаторе с появлением 0 на десятичном индикаторе.

Далее, соединим все остальные десятичные индикаторы с соответствующими сегментами семисегментного индикатора. Для некоторых логических элементов двух входов будет недостаточно, поэтому число входов следует увеличить, как показано на приведенной схеме:

Дешифраторы. Виды двоичных дешифраторов

Дешифраторы позволяют преобразовывать одни виды бинарных кодов в другие. Например, преобразовывать позиционный двоичный код в линейный восьмеричный или шестнадцатеричный. Преобразование производится по правилам, описанным в таблицах истинности, поэтому построение дешифраторов не представляет трудностей. Для построения дешифратора можно воспользоваться правилами синтеза логических схем для произвольной таблицы истинности.

Десятичный дешифратор

Рассмотрим пример разработки схемы дешифратора из двоичного кода в десятичный. Десятичный код обычно отображается одним битом на одну десятичную цифру. В десятичном коде десять цифр, поэтому для отображения одного десятичного разряда требуется десять выходов дешифратора. Сигнал с этих выводов можно подать на десятичный индикатор. В простейшем случае над светодиодом можно просто подписать индицируемую цифру.Таблица истинности десятичного дешифратора приведена в таблице 1.

Таблица 1. Таблица истинности десятичного дешифратора.

| Входы | Выходы | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 8 | 4 | 2 | 1 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Для реализации принципиальной схемы дешифратора воспользуемся методом СДНФ, так как в его таблице истинности на каждом выходе присутствует всего одна логическая единица. В результате получим схему дешифратора, реализующего таблицу истинности, приведённую в таблице 1. Эта схема приведена на рисунке 1.

Рисунок 1. Принципиальная схема двоично-десятичного дешифратора

Как видно по принципиальной схеме дешифратора, для реализации каждой строки таблицы истинности потребовался логический элемент «4И». Логические элементы «ИЛИ» не потребовались, так как в таблице истинности на каждом выходе присутствует только одна логическая единица.

Дешифраторы выпускаются в виде отдельных микросхем или используются в составе более сложных микросхем. В настоящее время десятичные или восьмеричные дешифраторы используются в основном как составная часть других микросхем, таких как мультиплексоры, демультиплексоры, ПЗУ или ОЗУ.

Условно-графическое обозначение микросхемы дешифратора на принципиальных схемах приведено на рисунке 2. На этом рисунке приведено обозначение двоично-десятичного дешифратора, полная внутренняя принципиальная схема которого изображена на рисунке 1.

Рисунок 2. Условно-графическое обозначение двоично-десятичного дешифратора

Точно таким же образом можно получить принципиальную схему и для любого другого декодера (дешифратора). Наиболее распространены схемы восьмеричных и шестнадцатеричных дешифраторов. Для индикации такие дешифраторы в настоящее время практически не используются. В основном такие дешифраторы используются как составная часть более сложных цифровых модулей.

Семисегментный дешифратор

Для отображения десятичных и шестнадцатеричных цифр часто используется семисегментный индикатор. Изображение семисегментного индикатора и название его сегментов приведено на рисунке 3.

Рисунок 3. Изображение семисегментного индикатора и название его сегментов

Для изображения на таком индикаторе цифры 0 достаточно зажечь сегменты a, b, c, d, e, f. Для изображения цифры ‘1’ зажигают сегменты b и c. Точно таким же образом можно получить изображения всех остальных десятичных или шестнадцатеричных цифр. Все комбинации таких изображений получили название семисегментного кода.

Составим таблицу истинности дешифратора, который позволит преобразовывать двоичный код в семисегментный. Пусть сегменты зажигаются нулевым потенциалом. Тогда таблица истинности семисегментного дешифратора примет вид, приведенный в таблице 2. Конкретное значение сигналов на выходе дешифратора зависит от схемы подключения сегментов индикатора к выходу микросхемы. Эти схемы мы рассмотрим позднее, в главе, посвящённой отображению различных видов информации.

Таблица 2. Таблица истинности семисегментного дешифратора

| Входы | Выходы | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 8 | 4 | 2 | 1 | a | b | c | d | e | f | g |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

В соответствии с принципами построения произвольной таблицы истинности по произвольной таблице истинности получим принципиальную схему семисегментного дешифратора, реализующего таблицу истинности, приведённую в таблице 2. На этот раз не будем подробно расписывать процесс разработки схемы. Полученная принципиальная схема семисегментного дешифратора приведена на рисунке 4.

Рисунок 4. Принципиальная схема семисегментного дешифратора

Для облегчения понимания принципов работы схемы на выходе логических элементов «И» показаны номера строк таблицы истинности, реализуемые ими.

Например, на выходе сегмента ‘a’ логическая единица появится только при подаче на вход комбинации двоичных сигналов 0001 (1) и 0100 (4). Это осуществляется объединением соответствующий цепей элементом «2ИЛИ». На выходе сегмента ‘b’ логическая единица появится только при подаче на вход комбинации двоичных сигналов 0101 (5) и 0110 (6), и так далее.

В настоящее время семисегментные дешифраторы выпускаются в виде отдельных микросхем или используются в виде готовых блоков составе других микросхем. Условно-графическое обозначение микросхемы семисегментного дешифратора приведено на рисунке 5.

Рисунок 5. Условно-графическое обозначение семисегментного дешифратора.

В качестве примера семисегментных дешифраторов можно назвать такие микросхемы отечественного производства как К176ИД3. В современных цифровых схемах семисегментные дешифраторы обычно входят в состав больших интегральных схем.

Понравился материал? Поделись с друзьями!

Вместе со статьей «Виды двоичных дешифраторов» читают: